XCV200-6FG456C FPGA: Functies, specificaties, programmeren en toepassingen

De XCV200-6FG456C is een krachtige FPGA (veldprogrammeerbare poortarray) uit de AMD Xilinx Virtex®-serie.Deze gids legt de functies, pin -lay -out, programmeerstappen en toepassingen uit.Met een hoog verwerkingsvermogen, flexibele ontwerpopties en sterke invoer/uitvoer (I/O) -mogelijkheden, helpt deze FPGA helpt bij het bouwen van snelle en betrouwbare digitale systemen.Of u nu werkt aan netwerken, besturingssystemen of aangepaste elektronica, deze handleiding helpt u te begrijpen hoe de XCV200-6FG456C in uw projecten kan worden gebruikt.Catalogus

XCV200-6FG456C overzicht

De XCV200-6FG456C is een opmerkelijk model binnen de AMD Xilinx Virtex® FPGA -familie, ontworpen om robuuste programmeerbare logische oplossingen te bieden voor complexe digitale systemen.Deze specifieke chip omvat ongeveer 236.666 systeempoorten en beschikt over 1.176 configureerbare logische blokken (CLB's) en 5.292 logische cellen.Het omvat ook 57.344 totale RAM-bits en ondersteunt 284 I/O-pinnen, gehuisvest in een 456-ball fijne ballengraster Array (FBGA) -pakket, meten van 23 mm x 23 mm.Dit model werkt op een 2,5V nominale spanning, met een bereik van 2,375 V tot 2,625V, en kan functioneren binnen een temperatuurbereik van 0 ° C tot 85 ° C.De bredere Virtex® -serie is geschikt voor een reeks toepassingen met dichtheden van 50.000 tot meer dan 1 miljoen systeempoorten en systeemkloktarieven tot 200 MHz.Het ondersteunt onder andere talloze I/O -normen, waaronder LVTTL, LVCMOS en PCI.Functies zoals vertragingsloten (DLL's), configureerbare logische blokken met ingebed geheugen en speciale draagmogica voor rekenkundige bewerkingen verbeteren de functionaliteit ervan.De Virtex®-familie is vervaardigd met behulp van een 5-lagen metaalproces van 0,22 µm, garandeert prestaties en betrouwbaarheid.

Als u FPGA-technologie van topklasse in uw producten of systemen wilt integreren, is het kopen van de XCV200-6FG456C in bulk met ons een slimme zet.Het voldoet aan de industriële normen en houdt u voor op toekomstige technologische behoeften.

XCV200-6FG456C Functies

• Systeempoorten: De XCV200-6FG456C biedt ongeveer 236.666 systeempoorten.Dit hoge poorttelling maakt de implementatie van complexe geïntegreerde digitale logische circuits op een enkele chip mogelijk, waardoor zowel prestaties als veelzijdigheid in een reeks toepassingen worden verbeterd.

• Logische bronnen: Het bevat 1.176 configureerbare logische blokken (CLB's) en 5.292 logische cellen.Deze bronnen zijn goed voor het ontwerpen van flexibele en schaalbare digitale circuits.CLB's kunnen worden geprogrammeerd om een breed scala aan logische functies uit te voeren, terwijl het grote aantal logische cellen de behandeling van uitgebreide logische bewerkingen en processen mogelijk maakt.

• Geheugen: Het apparaat biedt 57.344 bits RAM, verdeeld over de logische blokken.Dit ingebedde RAM wordt gebruikt voor toepassingen die snelle en efficiënte gegevensopslag en -opslag vereisen, ter ondersteuning van high-speed data-operaties die integraal zijn voor moderne digitale systemen.

• I/O -mogelijkheden: Met 284 ingang/uitgangspinnen vergemakkelijkt de XCV200-6FG456C uitgebreide interface-mogelijkheden.Deze I/O -pinnen ondersteunen verschillende signaalstandaarden en stellen de FPGA in staat om effectief te communiceren met andere componenten in een systeem, zoals geheugenapparaten, processors en randapparatuur.

• Spanning en temperatuurbereik: Werken met een nominale spanning van 2,5 V, met een acceptabel bereik van 2.375V tot 2.625V, deze FPGA is ontworpen voor low-power consumptie met behoud van robuuste prestaties.Het kan werken binnen een junctietemperatuurbereik van 0 ° C tot 85 ° C, waardoor de betrouwbaarheid onder verschillende omgevingscondities wordt gewaarborgd.

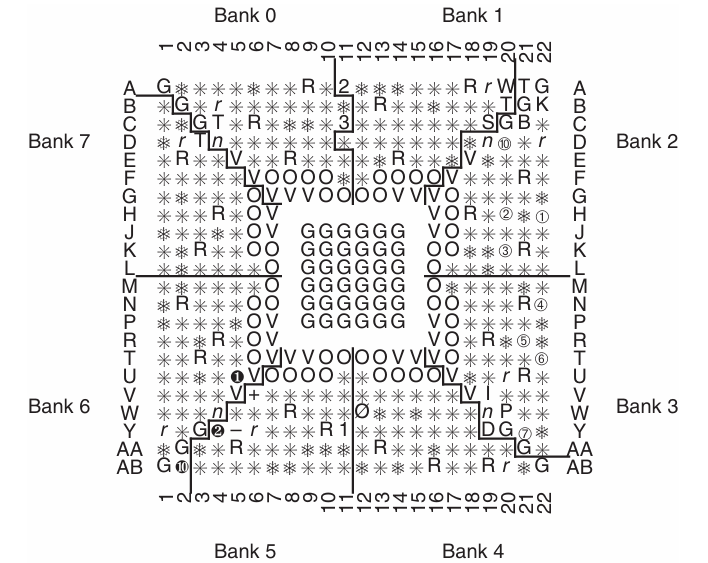

XCV200-6FG456C PIN-functiediagram

De XCV200-6FG456C PIN-functiediagram is een gestructureerde weergave van de PIN -toewijzingen van de FPGA, gecategoriseerd in verschillende banken (Bank 0 naar bank 7).Elke bankgroepen pins op basis van hun functie en fysieke plaatsing op het FPGA -pakket.Het nummerings- en etiketteringssysteem volgt een roosterpatroon waarbij rijen worden aangeduid met letters (A, B, C, enz.) En kolommen door getallen (1, 2, 3, enz.), Dat snelle identificatie van specifieke pennen vergemakkelijkt.Deze banken komen overeen met verschillende invoer-/uitvoerfuncties, vermogen, grond en speciale signaalroutering.Pinnen krijgen verschillende functionele groeperingen toegewezen, waaronder algemene I/O (GPIO), vaak gelabeld als "G" (algemene invoer/uitvoer), "V" (spanningsvoorraad) en "O" (uitgang).Power- en grondpennen zijn duidelijk gemarkeerd, waardoor stabiele FPGA -werking wordt gewaarborgd.Speciale purspinnen zoals klokinvoer, reset en besturingssignalen worden geïdentificeerd met symbolen zoals "R" of "T."Sommige pinnen dienen ook speciale communicatie-rollen, waaronder JTAG-configuratie en snelle klokken, voor programmeren en foutopsporing.

XCV200-6FG456C Blokdiagram

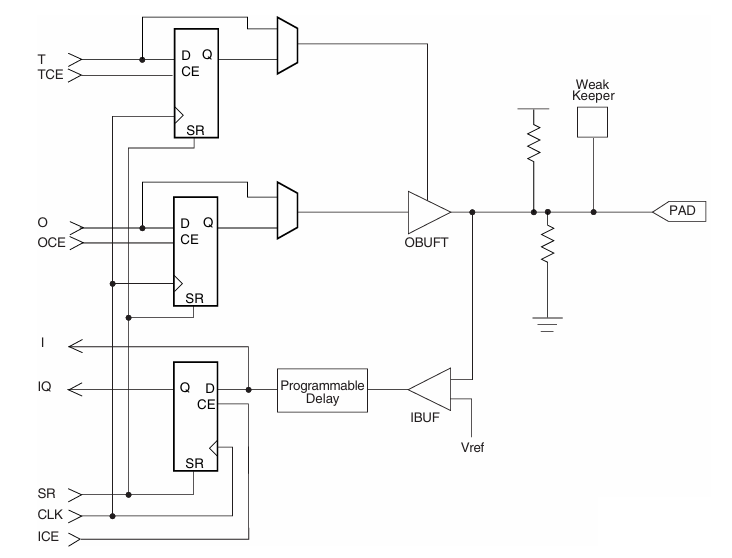

Input/uitgangsblok

Het diagram vertegenwoordigt de Input/Output Block (IOB) Structuur van de XCV200-6FG456C FPGA, die lid is van de Xilinx Virtex-familie.Het diagram toont belangrijke elementen die betrokken zijn bij invoer- en uitvoerbewerkingen, waarbij de gegevensstroom- en besturingsmechanismen worden benadrukt.In de kern van het diagram worden drie D-flip-flops gebruikt om signalen te registreren voor invoer-, uitgangs- en Tri-State-besturingselement.Het uitvoerregister wordt geregeld door het OCE (uitvoerklok Enable) -signaal, dat bepaalt wanneer de uitvoergegevens worden vergrendeld.Evenzo wordt het Tri-State-register bestuurd door de TCE (Tri-State Clock Enable), waardoor de uitgangsbuffer wordt ingeschakeld of uitgeschakeld.Het invoerregister legt inkomende gegevens vast en past een programmeerbare vertraging toe voordat het door de interne FPGA -logica wordt doorgegeven via de IBUF (invoerbuffer).De obufte (Tri-State-uitgangsbuffer) zorgt ervoor dat de FPGA een signaal op de kussen (I/O-pin) kan drijven of in een state met hoge impedanties kan plaatsen, afhankelijk van de besturingslogica.Een zwak keeper -circuit is opgenomen op het pad om de laatst bekende logische toestand te behouden wanneer er geen actieve bestuurder aanwezig is, waardoor onbedoelde zwevende omstandigheden worden voorkomen.De referentiespanning (VREF) wordt gebruikt voor bepaalde invoerstandaarden, zoals SSTL of HSTL, die precieze spanningsniveaus vereisen voor de juiste werking.Over het algemeen stelt deze IOB-structuur de FPGA in staat om high-speed gegevensoverdracht te beheren, verschillende I/O-normen te ondersteunen en flexibele controle te bieden over signaaltiming en integriteit.

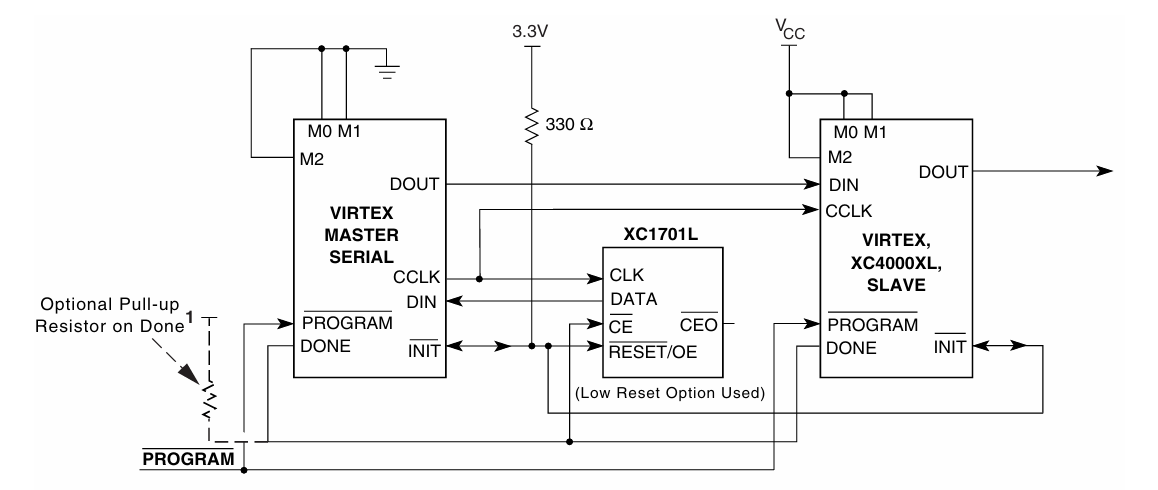

Master/slave seriële modus

De Master/slave seriële modus Blokdiagram illustreert het configuratieproces van een Virtex FPGA, met name de XCV200-6FG456C, wanneer geprogrammeerd in een Daisy-Chain-configuratie met behulp van een seriële EEPROM (XC1701L).In deze opstelling werkt één Virtex -apparaat als de master, waarbij de configuratieklok (CCLK) en serieel configuratiegegevens worden verzenden naar extra slave -fpgas in de keten.De master FPGA initieert het configuratieproces door het programmasignaal te beweren en alle apparaten in de keten te resetten.Zodra de initialisatie is voltooid, duidt het init -signaal de gereedheid aan en vloeit configuratiegegevensstromen van de seriële EEPROM (XC1701L) naar de DIN (data in) pin van de master FPGA.De master FPGA leest gegevens van de EEPROM en stuurt deze door via dout (gegevens uit) naar latere slave -fpGA's, die gegevensoverdracht synchroniseren met behulp van het CCLK -signaal.Het uitgevoerde signaal wordt gebruikt om een succesvolle configuratie aan te geven, met een optionele pull-up weerstand die zorgt voor een stabiele hoge toestand wanneer de configuratie is voltooid.De XC1701L EEPROM wordt bestuurd door de Master FPGA met behulp van CLK, Data, CE (CHIP Enable) en Reset/OE (uitvoer Enable) signalen, zodat de opgeslagen configuratiegegevens correct worden opgehaald.Deze configuratiemethode is efficiënt voor het programmeren van meerdere FPGA's met behulp van een enkele EEPROM, het verminderen van externe bedradingcomplexiteit en ervoor zorgen dat alle apparaten gesynchroniseerde configuratiegegevens ontvangen.

XCV200-6FG456C specificaties

|

Type |

Parameter |

|

Fabrikant |

AMD xilinx

|

|

Serie |

Virtex® |

|

Verpakking |

Dienblad |

|

Onderdeelstatus |

Verouderd |

|

Aantal laboratorium/CLB's |

1176 |

|

Aantal logische elementen/cellen |

5292 |

|

Totaal rambits |

57344 |

|

Aantal I/O |

284 |

|

Aantal poorten |

236666 |

|

Spanning - levering |

2.375V ~ 2.625V |

|

Montagetype |

Oppervlaktemontage |

|

Bedrijfstemperatuur |

0 ° C ~ 85 ° C (TJ) |

|

Pakket / kast |

456-BBGA |

|

Leverancierapparaatpakket |

456-FBGA (23x23) |

|

Base Productnummer |

XCV200 |

XCV200-6FG456C-toepassingen

Telecommunicatie en netwerken

De XCV200-6FG456C blinkt uit in telecommunicatie- en netwerktoepassingen vanwege de mogelijkheid om high-speed datatransmissies en complexe signaalverwerkingstaken af te handelen.De hoge poorttelling en robuuste I/O -mogelijkheden stellen het in staat om functies zoals pakketverwerking, signaalmodulatie/demodulatie en foutcorrectieprotocollen te ondersteunen.

Digitale signaalverwerking (DSP)

Ideaal voor DSP -applicaties kan deze FPGA snelle en complexe wiskundige berekeningen uitvoeren die nodig zijn in technologieën voor audio- en video -verwerking.Of het nu gaat om multimediasystemen, spraakherkenning of streamingdiensten, de krachtige verwerkingsmogelijkheden van de XCV200-6FG456C en ingebed geheugen ondersteunen efficiënte en hoogwaardige signaalverwerking.

Industriële controlesystemen

In de industriële automatisering biedt de XCV200-6FG456C de nodige prestaties om besturingssystemen en automatiseringsnetwerken te beheren.Het vermogen om meerdere besturingstaken tegelijkertijd uit te voeren en tegelijkertijd te zorgen voor responstijden, maakt het geschikt voor toepassingen in procescontrole, robotica en machine -visie.

Medische instrumenten

De precisie en snelheid van de FPGA zijn geweldig in medische beeldvorming en diagnostische apparatuur, waar het helpt bij de verwerking van complexe algoritmen voor beeldvormingstoepassingen zoals MRI, echografie en CT -scans.De mogelijkheden van de XCV200-6FG456C zorgen ervoor dat het hoge gegevensdoorvoer en ingewikkelde verwerking kan verwerken die nodig is in moderne medische technologie.

XCV200-6FG456C vergelijkbare onderdelen

XCV200-6FG456C programmeerstappen

Programmeerstappen voor de XCV200-6FG456C:

1. Ontwerpinvoer

De beginfase van FPGA -programmering omvat het definiëren van de digitale logica en functionaliteit van uw systeem.Dit kan worden gedaan met behulp van hardwarebeschrijving -talen (HDL's) zoals VHDL of Verilog, waar u code schrijft die aangeeft hoe de FPGA -gegevens verwerken en interageert met andere hardware.Schematische invoerhulpmiddelen die beschikbaar zijn in FPGA -ontwerpsoftware zoals Xilinx ISE of Vivado kan worden gebruikt.Deze methode omvat het maken van een visuele weergave van de logica door componenten te slepen en te laten vallen, die sommigen intuïtief vinden dan het schrijven van code.

2. Synthese

Zodra het ontwerp is voltooid, is de volgende stap synthese, waarbij een tool zoals Xilinx's XST (Xilinx -synthesetechnologie) uw HDL -code of schematisch ontwerp transformeert in een netlijst.Deze netlijst beschrijft het circuit in termen van generieke digitale componenten, zoals logische poorten en registers.Het syntheseproces omvat ook het optimaliseren van het ontwerp om te voldoen aan de prestatievereisten en het gebruik van bronnen voor efficiënte FPGA -werking te minimaliseren.

3. Implementatie

Het implementatieproces begint met vertaling en combineert uw ontwerp met beperkingsbestanden die parameters zoals klokfrequenties en pin -toewijzingen opgeven.Na vertaling wijst de kaartfase de elementen van uw netlijst toe aan specifieke fysieke bronnen op de FPGA, zoals opzoektafels (LUT's) en flip-flops.De plaatsing- en routeringsfase bepaalt vervolgens de fysieke locaties van elke component binnen de architectuur van de FPGA en legt de verbindingen tussen hen tot stand door programmeerbare interconnectbronnen.Deze fase is geweldig voor het bereiken van de gewenste prestatiestatistieken, inclusief klokfrequenties.

4. Bitstream -generatie

Na succesvolle plaatsing en routing genereert de tool een bitstream, een binair configuratiebestand dat alle programmeerinformatie voor de FPGA bevat.Het wordt vaak aanbevolen om het uiteindelijke ontwerp na de plaatsing te simuleren om ervoor te zorgen dat de bitstream zich zal gedragen zoals verwacht onder omstandigheden.Deze verificatiestap helpt om potentiële problemen tijdens de daadwerkelijke werking te voorkomen.

5. Configuratie

De laatste stap omvat het laden van de bitstream in de FPGA met behulp van verschillende configuratiemethoden.De slave-serie-modus, een eenvoudige en kosteneffectieve optie, configureert de FPGA via een extern masterapparaat dat gegevens serieel verzendt.In de master-serialodus leest de FPGA de bitstream autonoom van een bijgevoegd serieel prom.Voor hogesnelheidconfiguraties kan een SelectMap-modus een externe microprocessor snel in de FPGA laden.Bovendien wordt de JTAG-modus niet alleen gebruikt voor het programmeren, maar ook voor het testen en debuggen, met behulp van een standaardinterface voor programmering in het systeem en het testen van grensschalen.

XCV200-6FG456C Voordelen

Prestatie

De Xilinx Virtex-serie, waartoe de XCV200-6FG456C behoort, is geoptimaliseerd voor snelle prestaties en biedt systeemkloksnelheden tot 200 MHz.Dit maakt het goed geschikt voor toepassingen die snelle gegevensverwerking vereisen, waardoor een efficiënte behandeling van complexe algoritmen en snelle bewerkingen zoals telecommunicatie, verwerking en multimedia zorgt.

I/O -normenondersteuning

Deze FPGA ondersteunt een breed scala aan invoer/uitvoerstandaarden, waaronder LVTTL, LVCMOS, PCI, GTL, HSTL, SSTL, CTT en AGP.Dergelijke uitgebreide I/O-normenondersteuning stelt de XCV200-6FG456C in staat naadloos te integreren met verschillende systeemcomponenten, waardoor het nut ervan over diverse digitale ecosystemen wordt verbeterd.Deze flexibiliteit maakt het mogelijk om de FPGA aan te passen aan verschillende interface -omstandigheden zonder systeemaanpassingen.

Klokbeheer

De XCV200-6FG456C bevat meerdere vertragingslopen (DLL's) voor klokverdeling en -beheer binnen het systeem.Deze DLL's helpen bij het verbeteren van de systeemtiming en betrouwbaarheid door precieze kloksignalen te bieden die nodig zijn voor synchrone bewerkingen.Deze functie is belangrijk bij het verminderen van systeemfouten en het verbeteren van de algehele prestaties, met name in complexe ontwerpen die nauwkeurige timing en synchronisatie vereisen.

Ontwerpflexibiliteit

Met 1.176 configureerbare logische blokken en 5.292 logische cellen biedt de XCV200-6FG456C aanzienlijke logische bronnen met de mogelijkheid om een divers scala aan functionaliteiten te implementeren.Van eenvoudige lijmlogica tot ingewikkelde digitale systemen, deze FPGA ondersteunt complexe ontwerpvereisten, waardoor het ideaal is voor toepassingen in aangepaste computergebruik, digitale signaalverwerking en prototyping.

Snelle prototyping

FPGA's zoals de XCV200-6FG456C staan bekend om hun vermogen om snelle prototyping te ondersteunen.Dit apparaat zorgt voor snelle ontwerp iteraties en kan opnieuw worden geconfigureerd in het veld, wat een voordeel is voor ontwikkelingscycli omdat het tijd-tot-markt vermindert.Het past zich ook efficiënt aan aan het wijzigen van vereisten of updates in projectspecificaties, zodat de eindproducten up-to-date zijn met de nieuwste technologische normen.

Integratiemogelijkheden

De integratiemogelijkheden van de XCV200-6FG456C vergemakkelijken de consolidatie van meerdere discrete componenten in een enkele chip.Deze integratie kan leiden tot verminderde systeemcomplexiteit, lagere stroomverbruik en kostenbesparingen.Door het aantal benodigde afzonderlijke componenten te minimaliseren, vereenvoudigt deze FPGA ontwerpprocessen en verbetert de betrouwbaarheid en compactheid van het totale systeem.

XCV200-6FG456C verpakkingsafmetingen

De XCV200-6FG456C is een Field Programmable Gate Array (FPGA) uit AMD's Virtex®-serie, gehuisvest in een pakket met 456 ball ball grid array (FBGA).

• Pakkettype: 456-FBGA

• Pakketmaat: 23 mm x 23 mm

• Ball -pitch: 1,0 mm

XCV200-6FG456C fabrikant

De XCV200-6FG456C is een veldprogrammeerbare Gate Array (FPGA) die oorspronkelijk is ontwikkeld door Xilinx, een bedrijf dat bekend staat om zijn krachtige programmeerbare logische apparaten.Na de acquisitie van Xilinx door AMD, de XCV200-6FG456C is nu geassocieerd met AMD als de huidige fabrikant.Dit FPGA -model is echter verouderd en niet langer in productie.AMD blijft nieuwere FPGA -architecturen ondersteunen met verbeterde prestaties, krachtefficiëntie en langdurige levensduur, waardoor moderne alternatieven de voorkeur geven aan nieuwe ontwerpen.

Conclusie

De XCV200-6FG456C is een veelzijdige en snelle FPGA, nuttig voor veel technologische toepassingen.Hoewel het niet meer wordt gemaakt, is het nog steeds een goede keuze voor oudere systemen die betrouwbare prestaties nodig hebben.Deze gids heeft zijn ontwerp, programmeerstappen en praktisch gebruik behandeld, waardoor het gemakkelijker is om te begrijpen hoe het werkt en hoe het kan worden gebruikt.Naarmate nieuwere FPGA's beschikbaar komen, kunt u deze kennis gebruiken om de juiste FPGA voor uw behoeften te kiezen en digitale ontwerpen te verbeteren.

Datasheet PDF

XCV200-6FG456C datasheets:

Over ons

ALLELCO LIMITED

Lees verder

Quick Inviry

Stuur een aanvraag, we zullen onmiddellijk reageren.

Veel Gestelde Vragen [FAQ]

1. Wat is het stroomverbruik van de XCV200-6FG456C?

De XCV200-6FG456C werkt op 2,5 V, met een spanningsbereik van 2.375V tot 2.625V.Het stroomverbruik hangt af van het gebruik van logica en klokfrequentie, maar als een oudere FPGA kan het minder vermogensefficiënt zijn dan nieuwere Xilinx-apparaten.Juist krachtbeheer en warmtedissipatie moeten worden overwogen.

2. Hoe verhoudt de XCV200-6FG456C zich tot de XCV200-6FG256C?

De XCV200-6FG456C heeft een groter pakket (456-ball FBGA) vergeleken met de XCV200-6FG256C (256-ball FBGA), met meer I/O-pennen (284 versus 172) en potentieel betere prestaties voor toepassingen die uitgebreide interfacing vereisen.Als uw ontwerp afhankelijk is van meer I/O-mogelijkheden, is de XCV200-6FG456C de betere keuze.

3. Kan ik de XCV200-6FG456C meerdere keren herprogrammeren?

Ja, de XCV200-6FG456C is een op SRAM gebaseerde FPGA, wat betekent dat deze een onbeperkt aantal keren kan worden herprogrammeerd zolang de stroom wordt geleverd.U hebt echter extern niet-vluchtig geheugen (EEPROM of Flash) nodig om de bitstream na een stroomcyclus te behouden.

4. Ondersteunt de XCV200-6FG456C seriële communicatie met hoge snelheid?

De XCV200-6FG456C ondersteunt meerdere I/O-normen zoals LVTTL, LVCMOS, PCI, GTL, HSTL en SSTL, maar het heeft geen ingebouwde high-speed serdes (Serializer/Deserializer) of transceivers zoals moderne FPGA's.Voor toepassingen die high-speed seriële links vereisen (bijv. PCIe, Gigabit Ethernet of HDMI), overweeg dan nieuwere FPGA-modellen.

5. Hoe verhoudt de XCV200-6FG456C zich tot nieuwere FPGA-modellen?

De XCV200-6FG456C hoort bij een oudere generatie FPGA's.In vergelijking met moderne Virtex FPGAS heeft het een lagere telling, langzamere kloksnelheden en beperkte vermogensefficiëntie.Nieuwere modellen bieden een hogere logische dichtheid, meer ingebed geheugen, geavanceerde DSP -blokken en een lager stroomverbruik, waardoor ze beter worden voor moderne toepassingen.

AD73322ar Pinout, functies en technische details uitgelegd

Op 2025/03/21

EP20K100EFC324-1X FPGA: Functies, specificaties, toepassingen en programmeerhandleiding

Op 2025/03/20

Populaire berichten

-

Complexe instructieset computers: hoe ze de computer hebben gewijzigd?

Op 8000/04/18 147774

-

USB-C-pinout en functies

Op 2000/04/18 112011

-

Met behulp van Xilinx Unified Simulation Primitives: een uitgebreide gids voor FPGA -ontwerp en simulatie

Op 1600/04/18 111351

-

Voedingsspanningen in elektronica: betekenis van VCC, VDD, VEE, VSS en GND

Op 0400/04/18 83769

-

RJ45 -connectorhandleiding: pinout, bedrading, kabeltypen en gebruik

Op 1970/01/1 79565

-

De ultieme gids voor draadkleurcodes in moderne elektrische systemen

De manier waarop onze elektrische systemen kleuren gebruiken, is niet alleen voor uiterlijk.Elke draadkleur geeft nu een specifieke functie aan, waardoor het gemakkelijker wordt om elektrische comp...Op 1970/01/1 66960

-

PURGE VLEP GIDS: Functie, symptomen, testen en vervanging voor optimale motorprestaties

De Purge -klep is een belangrijk onderdeel van het systeem van een auto dat helpt de lucht schoon te houden door brandstofdampen te beheren voordat ze in de atmosfeer kunnen ontsnappen.Dit helpt ni...Op 1970/01/1 63100

-

Kwaliteit (Q) Factor: vergelijkingen en toepassingen

De kwaliteitsfactor, of 'Q', is belangrijk bij het controleren hoe goed inductoren en resonatoren werken in elektronische systemen die radiofrequenties gebruiken (RF).'Q' meet hoe goed een circuit ...Op 1970/01/1 63040

-

Piekprestaties bereiken met de maximale stelling van de stroomoverdracht

De maximale stelling van de stroomoverdracht legt uit hoe energie van een bron, zoals een batterij of generator, naar een aangesloten belasting stroomt.Het toont de exacte voorwaarde waar de belast...Op 1970/01/1 54097

-

A23 Batterijspecificaties en compatibiliteit

De A23-batterij is een kleine, cilindervormige batterij met hoge spanning.Ook wel 23A, 23ae of MN21 genoemd, het loopt op 12 volt en veel hoger dan AA- of AAA -batterijen.Het speciale ontw...Op 1970/01/1 52184