EP20K100EFC324-1X FPGA: Functies, specificaties, toepassingen en programmeerhandleiding

De EP20K100EFC324-1X is een programmeerbare chip (FPGA) uit Intel's Altera Apex-20Ke®-serie.Het is ontworpen om complexe digitale circuits aan te kunnen en ondersteunt snel gegevensverwerking.Deze gids legt zijn functies, specificaties, hoe het te programmeren en de voordelen ervan uitleggen, waardoor het een nuttige bron voor iedereen is.Catalogus

EP20K100EFC324-1X overzicht

De EP20K100EFC324-1X maakt deel uit van Intel's Altera Apex-20Ke®-serie, een veldprogrammeerbare Gate Array (FPGA) op maat gemaakt voor programmeerbare logische toepassingen met hoge dichtheid die geavanceerd systeem-op-een-programmeerbaar-chip (SOPC) integraties vereisen.Dit apparaat onderscheidt zich door de integratie van 4.160 logische elementen of cellen en 416 logische arrayblokken (laboratoria), die aanzienlijke configureerbaarheid voor verschillende digitale circuitontwerpen vergemakkelijken.Het beschikt ook over een aanzienlijk aantal ingebed geheugen dat de veeleisende vereisten voor gegevensopslag binnen de FPGA opvangt.De EP20K100EFC324-1X ondersteunt de veelzijdigheid van de toepassing verder en ondersteunt 246 I/O-pins en biedt een substantieel poort aantal van ongeveer 263.000 equivalente poorten, die efficiënt werken tussen 1,71V tot 1,89V.Het is verpakt in een 324-ball fine-pitch balletarray (FBGA), die helpt bij robuuste fysieke integratie in elektronische assemblages.

De EP20K100EFC324-1X is de perfecte keuze wanneer u klaar bent om bulkorders bij ons te plaatsen voor uw projecten of productlijnen.

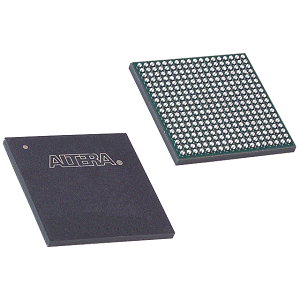

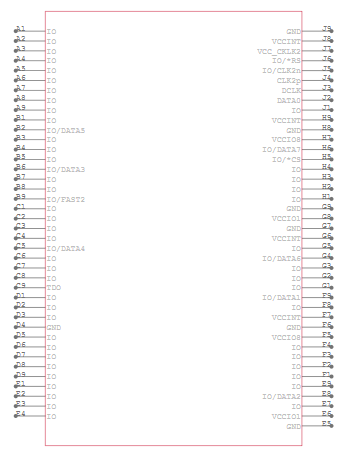

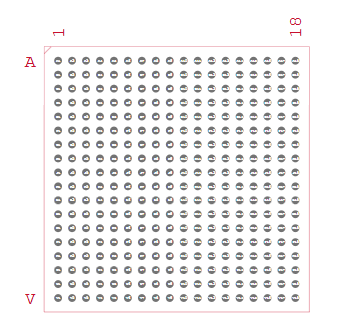

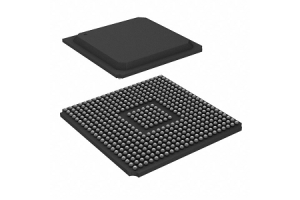

EP20K100EFC324-1X CAD-modellen

EP20K100EFC324-1X symbool

EP20K100EFC324-1X voetafdruk

EP20K100EFC324-1X 3D-model

EP20K100EFC324-1X Functies

• Hoge logische dichtheid: De FPGA is uitgerust met 4.160 logische elementen (LES) en 416 logische arrayblokken (laboratoria).Deze hoge dichtheid van logische cellen maakt het ontwerp en de uitvoering van complexe digitale circuits en systemen binnen een enkele chip mogelijk, waardoor het ideaal is voor toepassingen die robuuste logische verwerkingsmogelijkheden vereisen.

• Ingebed geheugen: Biedt 53.248 RAM -bits, deze FPGA biedt substantiële ingebedde geheugenbronnen.Deze functie is goed voor applicaties die snelle gegevensopslag en ophalen vereisen, waardoor een efficiënte behandeling van gegevensintensieve taken mogelijk is.

• Uitgebreide I/O -mogelijkheden: Met 246 invoer-/uitgangspinnen zorgt de EP20K100EFC324-1X voor uitgebreide connectiviteits- en interface-opties.Dit brede bereik van I/O -mogelijkheden stelt het in staat om eenvoudig verbinding te maken met een veelheid aan externe apparaten en systemen, waardoor het nut ervan in complexe elektronische assemblages wordt verbeterd.

• Multi-spanningsondersteuning: Het apparaat ondersteunt een kernspanningsbereik van 1,71 V tot 1,89 V en beschikt over Multivolt ™ I/O Interfacing.Hierdoor kan de FPGA compatibel zijn met andere elektronische componenten die op verschillende logische niveaus werken, waaronder 1,8 V, 2,5 V, 3,3 V en 5,0 V, wat een grote flexibiliteit biedt in systeemontwerp.

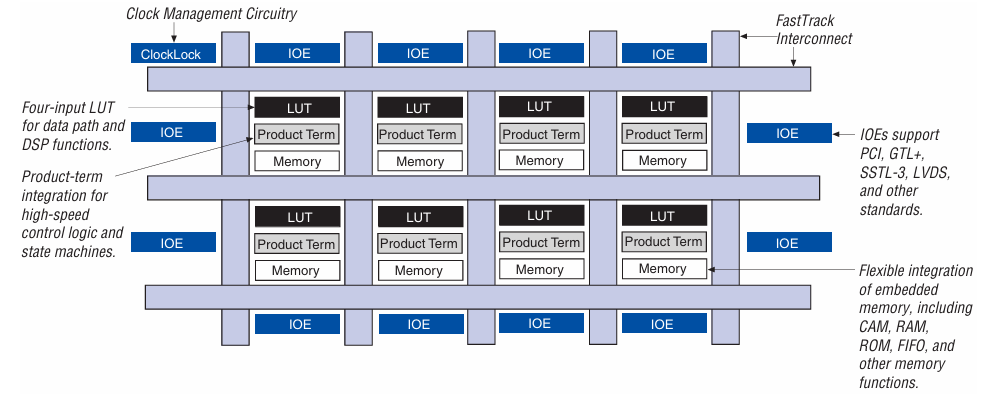

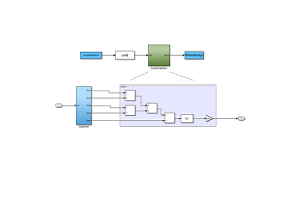

EP20K100EFC324-1X Blokdiagram

De EP20K100EFC324-1X Blokdiagram Vertegenwoordigt de interne structuur van een FPGA -apparaat (veldprogrammeerbaar gate -array), met de verschillende functionele eenheden.Het diagram bestaat uit onderling verbonden logische blokken, geheugenelementen, klokbeheer en I/O -elementen.In de kern van het ontwerp zijn Logica -arrayblokken (Labs), die bevatten Opzoektafels (LUTS) en op productetermijn gebaseerde logica.Deze elementen maken flexibele logische implementatie mogelijk, waardoor de FPGA geschikt is voor hogesnelheidsregellogica, statusmachines en DSP-functies.De Fasttrack interconnect Biedt een snelle communicatiepad tussen logische elementen, waardoor efficiënte signaalroutering op het hele apparaat wordt gewaarborgd.De Klokbeheercircuit , inclusief de ClockLock -functie, zorgt voor betrouwbare en gesynchroniseerde werking door kloksignalen over de FPGA te stabiliseren en te distribueren.De Input/output -elementen (IOES), geplaatst rond de FPGA -stof, dienen als interfaces voor externe communicatie.Deze IOE's ondersteunen meerdere industriestandaardprotocollen zoals PCI,, GTL+,, SSTL-3, En LVD's, waardoor de FPGA kan interface met verschillende externe systemen.Deze IOES zorgen voor compatibiliteit met verschillende spanningsniveaus en signaalnormen, waardoor de veelzijdigheid van de FPGA in ingebedde toepassingen wordt verbeterd. Ingebed geheugenblokken Bied flexibele opslagoplossingen binnen de FPGA.Deze geheugenelementen kunnen functioneren als Content Adresbaar geheugen (Cam), Random Access Memory (RAM), Alleen-lezen geheugen (ROM), Eerste-eerste uit (FIFO) buffers en andere geheugenstructuren.De mogelijkheid om geheugen rechtstreeks in de FPGA -stof te integreren, verbetert de efficiëntie van gegevensverwerking, waardoor externe geheugenafhankelijkheid en latentie worden verminderd.

EP20K100EFC324-1X specificaties

|

Type |

Parameter |

|

Fabrikant |

Intel |

|

Serie |

Apex-20Ke® |

|

Verpakking |

Dienblad |

|

Onderdeelstatus |

Verouderd |

|

Aantal laboratorium/CLB's |

416 |

|

Aantal logische elementen/cellen |

4160 |

|

Totaal rambits |

53248 |

|

Aantal I/O |

246 |

|

Aantal poorten |

263000 |

|

Spanning - levering |

1.71V ~ 1.89V |

|

Montagetype |

Oppervlaktemontage |

|

Bedrijfstemperatuur |

0 ° C ~ 85 ° C (TJ) |

|

Pakket / kast |

324-BGA |

|

Leverancierapparaatpakket |

324-FBGA (19x19) |

|

Base Productnummer |

EP20K100 |

EP20K100EFC324-1X-toepassingen

Netwerken en communicatie

Deze FPGA is ideaal voor netwerkapparatuur zoals routers en schakelaars, waar het gegevensroutering, signaalverwerking en protocolafhandeling beheert.De hoge logische dichtheid en uitgebreide I/O-mogelijkheden stellen het in staat om de complexe, snelle gegevensbewerkingen te ondersteunen die vereist zijn in de moderne communicatie-infrastructuur.

Industriële controlesystemen

In de industriële sector blinkt de EP20K100EFC324-1X uit in automatiseringssystemen.De programmeerbaarheid en robuuste verwerkingsmogelijkheden maken precieze controle en monitoring mogelijk voor het verbeteren van de operationele efficiëntie en betrouwbaarheid in productieprocessen.

Auto -elektronica

De FPGA dient als een component in autotoepassingen, met name in geavanceerde chauffeurssystemen (ADA's) en infotainmentsystemen in het voertuig.Het biedt de nodige verwerkingskracht en het aanpassingsvermogen om gegevens te verwerken en de geavanceerde functionaliteiten te ondersteunen die nodig zijn in moderne voertuigen.

Consumentenelektronica

Vanwege de flexibiliteit en hoge prestaties is de EP20K100EFC324-1X ook te vinden in consumentenelektronica zoals high-definition televisies en gameconsoles.Het ondersteunt complexe functionaliteiten en hulpmiddelen bij het verkorten van productontwikkelingscycli, en voldoet aan de snelle vraag naar de markt voor consumentenelektronica.

Medische hulpmiddelen

Op medisch gebied draagt deze FPGA bij aan de functionaliteit van medische beeldvormingsapparatuur en diagnostische hulpmiddelen.Het vermogen om gegevens met hoge snelheden te verwerken, zorgt ervoor dat deze apparaten nauwkeurige en tijdige diagnostische resultaten kunnen opleveren voor effectieve medische behandeling en beeldvorming.

EP20K100EFC324-1X vergelijkbare onderdelen

EP20K100EFC324-1X programmeerstappen

Om de EP20K100EFC324-1X, een lid van de APEX-20KE® FPGA-serie van Altera, effectief te programmeren, is het belangrijk om een gestructureerde reeks stappen te volgen.Dit proces zorgt ervoor dat uw ontwerp efficiënt wordt vertaald in een formaat dat de FPGA kan uitvoeren.Hieronder schet ik een gedetailleerde aanpak voor het programmeren van dit FPGA -model, stappen en wijzigingen integreren die specifiek zijn voor dit apparaat.

1. Ontwerpinvoer

Begin met het maken van uw digitale logica -ontwerp.Gebruik hardwarebeschrijving talen (HDL's) zoals VHDL of Verilog, waarmee u de hardwarefunctionaliteit en logica van uw systeem kunt beschrijven.Tools zoals Quartus II van Altera bieden een uitgebreide omgeving voor het schrijven, testen en samenstellen van uw HDL -code.Zorg ervoor dat uw ontwerp modulair is, waardoor het gemakkelijker is om te debuggen en te schalen.

2. Synthese

Zodra uw ontwerpitem is voltooid, is de volgende stap synthese, waarbij de HDL -code wordt vertaald in een netlijst.Deze netlijst vertegenwoordigt de onderling verbonden lijst van poorten, slippers en andere hardware-elementen die uw ontwerp vormen.Tijdens de synthese is de code geoptimaliseerd voor de specifieke architectuur van de EP20K100EFC324-1X, zodat het ontwerp de bronnen van de FPGA effectief gebruikt.Tools zoals Synplify Pro of het synthesetool in Quartus II kunnen voor dit doel worden gebruikt.Het is belangrijk om je te concentreren op het optimaliseren van uw ontwerp om te voldoen aan timing- en resource -beperkingen.

3. Implementatie

Na synthese vindt implementatie plaats.Deze stap omvat het in kaart brengen van de netlijst aan de werkelijke FPGA -hardware.Het omvat de plaatsing van de logische elementen binnen de FPGA en de routing van de verbindingen daartussen.De Quartus II -software faciliteert dit proces via de implementatiehulpmiddelen, die de plaatsing en routing beheren om te voldoen aan de gewenste kloksnelheden en prestatiestatistieken.Tijdens de implementatie moet u mogelijk uw ontwerp herhalen op basis van de feedback van timinganalysetools om ervoor te zorgen dat aan alle prestatievereisten wordt voldaan.

4. Bitstream -generatie

Na een succesvolle implementatie genereert de volgende fase de bitstream.Dit is het binaire bestand dat op de FPGA wordt geladen.De bitstream bevat geconfigureerde gegevens voor elk programmeerbaar element in de FPGA, waarbij het apparaat wordt ingesteld om de functies uit te voeren volgens uw ontwerp.De Quartus II -software kan deze bitstream genereren, die vervolgens klaar is om te worden gedownload naar de FPGA.

5. De FPGA programmeren

De laatste stap is om de FPGA te programmeren met de gegenereerde bitstream.Dit kan worden gedaan met behulp van een hardwareprogrammeur die compatibel is met de EP20K100EFC324-1X, zoals de USB-blaster.Sluit de programmeur aan op uw ontwikkelingsbord waar de FPGA is gemonteerd en gebruik het Quartus II -programmeermiddel om de bitstream naar de FPGA over te dragen.Deze stap laadt uw ontwerp op de FPGA en begint te werken volgens de logica die is gedefinieerd in uw HDL -code.

EP20K100EFC324-1X Voordelen

Hoge integratie

De EP20K100EFC324-1X biedt hoge integratiemogelijkheden vanwege het grote aantal logische elementen en ingebed geheugen.Deze integratie maakt het mogelijk om meerdere functionaliteiten in één apparaat te consolideren.Als gevolg hiervan kunnen systemen worden vereenvoudigd, waardoor het totale aantal componenten, de vereiste fysieke ruimte en potentiële faalpunten in elektronische ontwerpen worden verminderd.

Flexibele logica -implementatie

De architectuur van de EP20K100EFC324-1X ondersteunt zowel opzoektabel (LUT) als op productetermijn gebaseerde logica.Deze flexibiliteit in logische implementatie maakt het mogelijk om de FPGA te optimaliseren voor een breed scala aan toepassingen, van eenvoudige logische poorten tot complexe combinatiecircuits.Het biedt een voordeel in termen van ontwerpverkenbaarheid en biedt plaats aan een breed spectrum van digitale functionaliteiten.

Geavanceerde interconnectstructuur

Met een hiërarchische interconnectstructuur omvat de FPGA Local, Megalab ™ en FastTrack® -interconnecties.Deze gespecialiseerde routeringsbronnen verbeteren de efficiëntie van de signaalroutering en verbeteren de algehele prestaties van het apparaat.Deze geavanceerde interconnectstructuur is goed voor ontwerpen die een snelle gegevensoverdracht en lage latentie vereisen, waardoor de FPGA ideaal is voor high-performance computing en telecommunicatie.

Klokbeheer

De EP20K100EFC324-1X omvat ClockLock- en ClockBoost-technologie, die helpt bij effectief klokbeheer.Deze functies helpen bij het handhaven van de integriteit van het kloksignaal gedurende de FPGA, het verminderen van jitter en het verbeteren van de signaalbetrouwbaarheid.Effectief klokbeheer is nodig voor synchrone digitale circuits, waardoor stabiele en voorspelbare werking wordt gewaarborgd over verschillende omgevingscondities.

Ontwerpflexibiliteit

De programmeerbare aard van de EP20K100EFC324-1X maakt het mogelijk om hardware op specifieke behoeften aan te passen en de FPGA opnieuw te configureren voor verschillende toepassingen of updates.Deze flexibiliteit betekent dat een enkele FPGA kan worden gebruikt voor meerdere projecten, wat gunstig is in een dynamisch technologisch landschap waar de vereisten snel kunnen veranderen.

Snelle prototyping

FPGAS zoals de EP20K100EFC324-1X maakt snelle prototyping van digitale circuits mogelijk.U kunt ontwerpen snel ontwikkelen en herhalen zonder de lange doorlooptijden die verband houden met aangepaste ASIC -ontwikkeling.Dit vermogen om snel nieuwe ontwerpen te modelleren en te testen, versnelt het ontwikkelingsproces, wat leidt tot snellere innovatie en een verkorte tijd-tot-markt.

Kostenefficiëntie

Het integreren van meerdere functies binnen een enkele FPGA vermindert de behoefte aan extra discrete componenten, wat kan leiden tot kostenbesparingen in zowel inkoop als assemblage.Deze integratie vereenvoudigt ook het productieproces en kan de algehele systeemcomplexiteit verminderen, wat leidt tot lager onderhoud en de kosten van het product over de levenscyclus van het product.

Langdurige ondersteuning

Het herconfigureerbare aspect van de EP20K100EFC324-1X zorgt ervoor dat hardware kan worden bijgewerkt om bugs te repareren, de prestaties te verbeteren of nieuwe functies toe te voegen zonder fysieke hardwareveranderingen te vereisen.Deze langetermijnondersteuning en aanpassingsvermogen beschermen investeringen en stellen apparaten in staat om relevant te blijven naarmate er nieuwe normen en technologieën ontstaan.

EP20K100EFC324-1X verpakkingsafmetingen

De EP20K100EFC324-1X is een FPGA uit Altera's Apex-20Ke®-serie, gehuisvest in een 324-ball Fine-Pitch Ball Grid Array (FBGA) pakket.De verpakkingsafmetingen zijn als volgt:

• Toonhoogte: 1 mm

• Lengte × breedte: 19 mm × 19 mm

• Gebied: 361 mm²

EP20K100EFC324-1X fabrikant

De EP20K100EFC324-1X is een model uit de APEX-20KE®-serie van Field Programmable Gate Arrays (FPGA's) die oorspronkelijk door Altera zijn ontwikkeld.Na de acquisitie van Altera door Intel in 2015, werden deze FPGA- en andere Altera -producten onderdeel van Intel's uitgebreide programmeerbare oplossingsportfolio.Als gevolg hiervan, Intel Blijft de productlijnen van Altera ondersteunen terwijl ze worden geïntegreerd met hun eigen geavanceerde technologieaanbod.Hoewel de EP20K100EFC324-1X als verouderd is geclassificeerd en niet langer in productie is, wordt de erfenis onder Intel gehandhaafd, die nieuwere FPGA-modellen aanbeveelt voor huidige toepassingen om ondersteuning en beschikbaarheid op lange termijn te garanderen.

Conclusie

De EP20K100EFC324-1X is een krachtige en flexibele FPGA waarmee aangepaste digitale circuits kunnen worden gemaakt en testen.Het biedt hoge prestaties, ingebouwd geheugen en multi-spanningsondersteuning, waardoor het nuttig is in veel industrieën.Deze gids heeft u door de belangrijkste functies, het ontwerp en de stappen gebracht om deze FPGA op een eenvoudige manier te programmeren, zodat u deze gemakkelijk kunt begrijpen en gebruiken.

Datasheet PDF

EP20K100EFC324-1X datasheets:

Over ons

ALLELCO LIMITED

Lees verder

Quick Inviry

Stuur een aanvraag, we zullen onmiddellijk reageren.

Veel Gestelde Vragen [FAQ]

1. Hoe verhoudt de EP20K100EFC324-1X zich tot nieuwere FPGA-modellen?

De EP20K100EFC324-1X blijft een krachtige FPGA voor legacy-systemen en industriële toepassingen die een hoge logische dichtheid en flexibele I/O-mogelijkheden vereisen.In vergelijking met moderne FPGA's zoals Intel's cycloon-, arria- of Stratix-serie mist het echter geavanceerde vermogensefficiëntie, hogesnelheidszuinigers en AI-aangedreven versnelling.Als u een nieuw systeem ontwerpt, kunnen we equivalente of opgewaardeerde modellen voorstellen.

2. Ondersteunt de EP20K100EFC324-1X externe geheugeninterfaces zoals DDR of SRAM?

Ja, de EP20K100EFC324-1X ondersteunt externe geheugeninterfaces, waaronder SRAM en SDRAM.Het ondersteunt echter niet native DDR2/DDR3.Als high-speed geheugeninterface vereist is, kan extra externe logica of een nieuwere FPGA nodig zijn.

3. Kan ik de EP20K100EFC324-1X meerdere keren opnieuw configureren?

Ja, zoals alle FPGA's, is dit apparaat volledig herprogrammeerbaar.Als u echter een vluchtige configuratie gebruikt, heeft u een extern geheugen (zoals een serieel prom) nodig om het ontwerp te behouden na stroomfietsen.

4. Kan ik de EP20K100EFC324-1X programmeren met behulp van Intel Quartus-software?

Ja, u kunt de EP20K100EFC324-1X programmeren met behulp van Intel Quartus II (Legacy Versions), omdat deze FPGA tot de APEX-20KE®-familie behoort.Zorg ervoor dat uw Quartus II -versie dit apparaat ondersteunt, omdat nieuwere Quartus Prime -edities geen Legacy FPGA's ondersteunen.

5. Welke voedingsvereisten moet ik overwegen bij het gebruik van de EP20K100EFC324-1X?

De EP20K100EFC324-1X werkt met een kernspanningsbereik van 1,71 V tot 1,89V.Het beschikt ook over multivolt ™ I/O -technologie, die 1,8 V-, 2,5 V-, 3,3V -en 5,0 V -logische niveaus ondersteunt.Zorg ervoor dat uw voeding voldoet aan deze spanningsvereisten voor stabiele prestaties.

XCV200-6FG456C FPGA: Functies, specificaties, programmeren en toepassingen

Op 2025/03/20

Waarom 0603 componenten populair zijn in moderne elektronica

Op 2025/03/20

Populaire berichten

-

Complexe instructieset computers: hoe ze de computer hebben gewijzigd?

Op 8000/04/17 147718

-

USB-C-pinout en functies

Op 2000/04/17 111774

-

Met behulp van Xilinx Unified Simulation Primitives: een uitgebreide gids voor FPGA -ontwerp en simulatie

Op 1600/04/17 111327

-

Voedingsspanningen in elektronica: betekenis van VCC, VDD, VEE, VSS en GND

Op 0400/04/17 83645

-

RJ45 -connectorhandleiding: pinout, bedrading, kabeltypen en gebruik

Op 1970/01/1 79318

-

De ultieme gids voor draadkleurcodes in moderne elektrische systemen

De manier waarop onze elektrische systemen kleuren gebruiken, is niet alleen voor uiterlijk.Elke draadkleur geeft nu een specifieke functie aan, waardoor het gemakkelijker wordt om elektrische comp...Op 1970/01/1 66798

-

Kwaliteit (Q) Factor: vergelijkingen en toepassingen

De kwaliteitsfactor, of 'Q', is belangrijk bij het controleren hoe goed inductoren en resonatoren werken in elektronische systemen die radiofrequenties gebruiken (RF).'Q' meet hoe goed een circuit ...Op 1970/01/1 62963

-

PURGE VLEP GIDS: Functie, symptomen, testen en vervanging voor optimale motorprestaties

De Purge -klep is een belangrijk onderdeel van het systeem van een auto dat helpt de lucht schoon te houden door brandstofdampen te beheren voordat ze in de atmosfeer kunnen ontsnappen.Dit helpt ni...Op 1970/01/1 62852

-

Piekprestaties bereiken met de maximale stelling van de stroomoverdracht

De maximale stelling van de stroomoverdracht legt uit hoe energie van een bron, zoals een batterij of generator, naar een aangesloten belasting stroomt.Het toont de exacte voorwaarde waar de belast...Op 1970/01/1 54045

-

A23 Batterijspecificaties en compatibiliteit

De A23-batterij is een kleine, cilindervormige batterij met hoge spanning.Ook wel 23A, 23ae of MN21 genoemd, het loopt op 12 volt en veel hoger dan AA- of AAA -batterijen.Het speciale ontw...Op 1970/01/1 52025