XC2S100E-6FTG256C FPGA Guide: specificaties, functies en toepassingen

Deze gids onderzoekt de XC2S100E-6FTG256C, een kosteneffectieve en veelzijdige FPGA die is ontworpen voor ingebedde systemen, industriële controle en digitale logische toepassingen.Met een rijke combinatie van logische cellen, blok en gedistribueerde RAM en hoge I/O -flexibiliteit, dient het als een betrouwbare oplossing voor zowel moderne toepassingen als legacy -systeemondersteuning.In deze gids leer je wat deze FPGA kan doen, hoe het is gebouwd, hoe het te gebruiken en waarom het vandaag nog steeds een goede keuze is.Catalogus

XC2S100E-6FTG256C Overzicht

De XC2S100E-6FTG256C is een krachtige, goedkope FPGA van Spartan-Iie-familie, op maat gemaakt voor ingebedde systemen, industriële automatisering en legacy digitale verwerkingsontwerpen.Met een capaciteit van 100.000 systeempoorten en 2.700 logische cellen ondersteunt dit apparaat veelzijdige logische toepassingen met behoud van een efficiënt stroomverbruik door zijn 1,8V -kern.Het bevat 40 kbits blok RAM en 38.400 bits gedistribueerde RAM, die ontwerpers flexibele geheugenconfiguraties biedt.Werken met snelheden tot 275 MHz, ondersteunt het snelle gegevensverwerking voor tijdkritische taken.Ontworpen met behulp van 0,15 µm CMOS -technologie, duidt de -6 -snelheidsgraad aan een betrouwbare prestatielaag die geschikt is voor de meeste reguliere toepassingen.De Spartan-IIE-familie, die de XC2S100E-6FTG256C, Ranges in logic-dichtheid omvat van 50K tot 600K-poorten en functies benodigde tools zoals vier DLL's voor geavanceerde klokcontrole, speciale draaglogica voor rekenkundige functies en compatibiliteit met 3,3V PCI/CardBus-interfaces.

Als u op zoek bent naar betrouwbare FPGA-oplossingen, is de XC2S100E-6FTG256C een solide keuze

XC2S100E-6FTG256C Functies

Logische capaciteit: De XC2S100E-6FTG256C biedt 100.000 systeempoorten en biedt voldoende logica voor matig complexe digitale ontwerpen.De 2.700 logische cellen dienen als de kernconfigureerbare logische blokken die een breed scala aan door de gebruiker gedefinieerde functies mogelijk maken.

Ingebed geheugen: Deze FPGA omvat 40 kbits synchrone blok RAM, geschikt voor buffering, tijdelijke gegevensopslag of het implementeren van FIFO's en andere geheugenstructuren in het logische ontwerp.

Gedistribueerd ram: Naast blok RAM biedt het 38.400 bits gedistribueerde RAM die kunnen worden gebruikt voor compacte geheugenelementen die zich over de logische stof verspreiden.Dit is handig voor het implementeren van kleine opzoektabellen of configuratiegegevens in de buurt van de verwerkingslogica.

Gebruiker I/O -pinnen: Het apparaat biedt maximaal 176 algemene I/O-pinnen, waardoor het kan communiceren met een breed scala aan randapparatuur, externe geheugenapparaten of andere IC's in het systeem.

Hoge bedrijfsfrequentie: Met een maximale interne kloksnelheid van 275 MHz maakt de XC2S100E snelle signaalverwerking mogelijk en ondersteunt ze snelle bewerkingen die nodig zijn in besturingssystemen, communicatie en signaalverwerving.

Kernspanning: Werken met een kernspanning van 1,8 V, het apparaat is ontworpen voor een laag stroomverbruik, terwijl het nog steeds voldoende prestaties behoudt voor middelentoepassingen.

Procestechnologie: Vervaardigd met behulp van een CMOS-proces van 0,15 micron, evenwicht dit apparaat de integratiedichtheid met thermische efficiëntie en biedt een stabiele werking onder industriële omstandigheden.

Snelheidsgraad: De "-6" snelheidsgraad duidt op de standaardprestatievariant binnen de Spartan-IIE-serie.Het biedt een uitgebalanceerde combinatie van snelheid en vermogensefficiëntie die geschikt is voor een breed scala aan digitale ontwerpen.

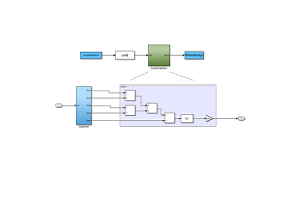

XC2S100E-6FTG256C Blokdiagram

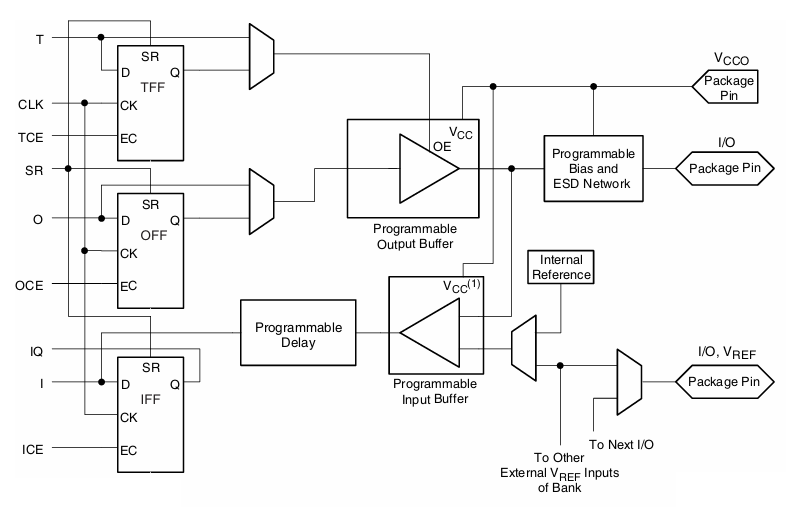

Input/Output Block (IOB)

Dit diagram laat zien hoe de XC2S100E-6FTG256C FPGA signalen verwerkt die in en uit zijn I/O-pinnen gaan.Met het invoer/uitvoerblok (IOB) kunt u bepalen wanneer en hoe gegevens beweegt tussen de FPGA en de buitenwereld.Het heeft afzonderlijke secties voor invoer-, uitvoer- en besturingslogica.Aan de uitvoerzijde komen signalen van slippers (TFF en UIT), die de gegevens opslaan.Deze worden bestuurd door een klok (CLK), schakel signalen (TCE, OCE) en een set/reset -ingang (SR) in.De uitvoergegevens gaan door een programmeerbare buffer die het signaal naar de pin drijft.Deze buffer kan worden afgestemd op sterkte en snelheid en omvat bescherming tegen statische elektriciteit (ESD).Voor ingangen passeren signalen van de pin een vertragingsblok en vervolgens een programmeerbare invoerbuffer.Deze buffer kan aanpassen hoe het het signaal leest, afhankelijk van de spanningsniveaus en normen.Een referentiespanning (VREF) helpt het te beslissen hoe de invoer te verwerken, vooral bij het gebruik van bepaalde signaaltypen.

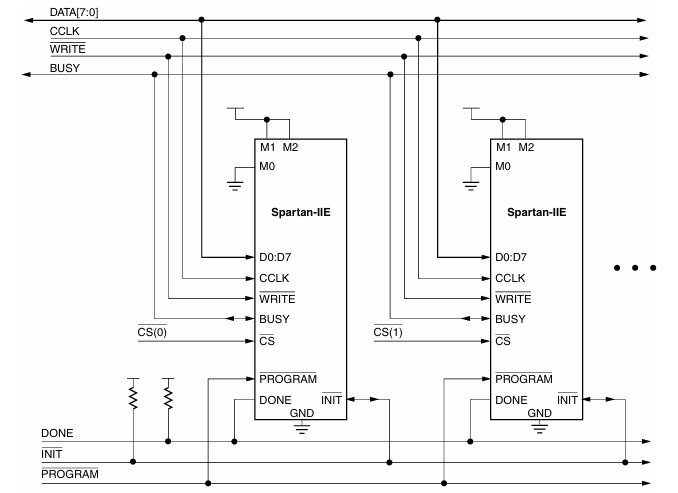

Slaven parallelle modus

Het diagram illustreert de Slave Parallel Mode-configuratie voor meerdere XC2S100E-6FTG256C Spartan-Iie FPGAS van AMD Xilinx.In deze opstelling worden verschillende FPGA's tegelijkertijd geprogrammeerd met behulp van een gedeelde 8-bit gegevensbus (gegevens [7: 0]), een gemeenschappelijke configuratieklok (CCLK) en controlesignalen zoals schrijven en programma.Elke FPGA ontvangt de configuratiegegevens parallel, waardoor snellere programmering mogelijk is in vergelijking met seriële modi.

Elke FPGA heeft zijn M0-M2-moduspennen geaard, waardoor deze in de slave-parallelle modus wordt gesteld, waarbij de configuratiegegevens door een externe controller in het apparaat worden geduwd.De CS -lijn (CHIP Select) wordt gebruikt om individuele apparaten in te schakelen, waardoor slechts één FPGA actief is tijdens de configuratie om de stelling van de bus te voorkomen.De drukke en gedaan signalen helpen de status van elk apparaat tijdens het proces te bewaken, terwijl de init -pin wordt gedeeld om de initialisatie op alle apparaten te coördineren.Pull-up weerstanden op Done en Init zorgen voor de juiste logische niveaus wanneer inactief.

XC2S100E-6FTG256C specificaties

|

Type |

Parameter |

|

Fabrikant |

AMD/Xilinx |

|

Serie |

Spartan®-iie |

|

Verpakking |

Dienblad |

|

Onderdeelstatus |

Verouderd |

|

Aantal laboratorium/CLB's |

600 |

|

Aantal logische elementen/cellen |

2700 |

|

Totaal rambits |

40960 |

|

Aantal I/O |

182 |

|

Aantal poorten |

100000 |

|

Spanning - levering |

1.71V ~ 1.89V |

|

Montagetype |

Oppervlaktemontage |

|

Bedrijfstemperatuur |

0 ° C ~ 85 ° C (TJ) |

|

Pakket / kast |

256-lbga |

|

Leverancierapparaatpakket |

256-ftbga (17x17) |

|

Base Productnummer |

XC2S100E |

XC2S100E-6FTG256C-toepassingen

Industriële automatiserings- en besturingssystemen

De XC2S100E-6FTG256C is ideaal voor het implementeren van logica-intensieve controleschema's in industriële omgevingen.Het kan signaalverwerking, motorbesturingslussen en programmeerbare logica beheren voor robotica en productiesystemen.De snelle I/O en betrouwbare timing maken het geschikt voor het interface met sensoren, actuatoren en toezichtcontrollers.

Embedded Systems en SOC -prototyping

Met deze FPGA kunt u aangepaste ingebedde logische platforms en prototypesystem-on-chip (SOC) architecturen maken.Met herprogrammeerbare logica en gedistribueerd geheugen helpt het de verwerkingskernen, perifere interfaces en aangepaste digitale IP -blokken snel en betaalbaar te simuleren.

Auto -elektronica

Het apparaat kan worden gebruikt in voertuigen voor taken zoals het beheren van digitale dashboards, entertainmentsystemen in voertuigen en signaalverwerking op laag niveau in systemen voor bestuurder.De krachtefficiëntie en robuuste I/O-ondersteuning passen bij de ontwerpen van auto's die de betrouwbaarheid op lange termijn vereisen.

Educatieve en trainingsplatforms

Met zijn benaderbare logische dichtheid en toegankelijke toolchain (ISE Design Suite), is de XC2S100E-6FTG256C uitstekend voor het leren van digitaal ontwerp, VHDL/Verilog-programmering en systeemintegratietechnieken.

Legacy System Maintenance and Upgrades

Veel systemen gebouwd in de vroege jaren 2000 gebruikten SPARTAN-IIE FPGAS zoals deze.De XC2S100E-6FTG256C blijft goed voor het ondersteunen en onderhouden van deze systemen, waardoor reparatie of verbetering mogelijk is zonder volledig herontwerp, waardoor software en hardwarecompatibiliteit wordt gewaarborgd.

XC2S100E-6FTG256C vergelijkbare onderdelen

De XC2S100E-6PQG208C is lid van dezelfde Spartan-Iie-familie en biedt dezelfde logische capaciteit en prestatiespecificaties als de XC2S100E-6FTG256C, inclusief 2.700 logische cellen en 100.000 systeempates.Het is verpakt in een 208-pins plastic quad flat-pack (PQFP), waardoor het geschikt is voor ontwerpen die de voorkeur geven aan of vereisen van loodpakketten voor eenvoudiger inspectie en herwerken.Het is een sterk alternatief als u weggaat van BGA-verpakkingen en een goedkopere of gemakkelijker te solder voetafdruk nodig hebt met behoud van volledige functionele equivalentie.

Dit deel is vrijwel identiek aan de XC2S100E-6PQG208C, voornamelijk verschillend in mogelijke markeringen of sourcing, maar nog steeds gehuisvest in hetzelfde 208-pins PQFP-pakket.Het behoudt dezelfde -6 snelheidsgraad en elektrische prestaties, waardoor het een drop -in alternatief is in termen van logisch gedrag voor ontwerpen die al de PQ208 -voetafdruk gebruiken.Deze optie is uitstekend wanneer sourcing flexibiliteit nodig is, omdat het compatibiliteit mogelijk maakt met dezelfde PCB -lay -out terwijl het uw leverancieropties uitbreidt.

De XC2S100E-6FT256C deelt de exacte BGA-pin-telling (256 ballen) als de originele XC2S100E-6FTG256C, hoewel het enigszins kan verschillen in thermische of verpakkingsspecificaties (bijv. "FT" versus "FTG").Elektrisch en functioneel is het bijna identiek, en omdat het binnen dezelfde BGA -categorie en logische familie blijft, is het de meest directe vervanging vanuit een mechanisch en prestatiebestendigheid.Als u op zoek bent naar minimaal PCB -herontwerp, is dit deel waarschijnlijk de meest naadloze vervanging.

XC2S100E-6FTG256C programmeerstappen

1. Ontwerpinvoer en synthese: Om te beginnen met het programmeren van de XC2S100E-6FTG256C, moet u eerst het digitale logische ontwerp maken met behulp van een hardwarebeschrijving Language (HDL) zoals VHDL of Verilog.Deze stap wordt uitgevoerd met behulp van de Xilinx ISE -ontwerpsuite of een vergelijkbare synthesetool.Na het schrijven van het ontwerp wordt het gesynthetiseerd om de logica op hoog niveau om te zetten in een netlijst op een poortniveau.De synthesetool genereert vervolgens een bitstream -bestand (meestal met een .bit -extensie), die de configuratiegegevens bevat die nodig zijn om de FPGA te programmeren.

2. Selecteer de configuratiemodus: De Spartan-Iie-familie ondersteunt verschillende configuratiemodi, waaronder slavenserie, master serial, slave parallel, master parallel en jtag (grensscan).U moet de modus selecteren die past bij uw systeeminstelling door de moduspennen correct in te stellen (M0, M1, M2).Deze pinnen bepalen hoe de FPGA zijn configuratiegegevens zal laden na aan / uit-up of reset.De JTAG-modus wordt bijvoorbeeld meestal gebruikt voor debugging en flexibiliteit in het systeem tijdens de ontwikkeling.

3. Verbind programmeerhardware: Afhankelijk van de geselecteerde configuratiemodus, sluit u de juiste hardware aan.Gebruik voor JTAG -programmering een JTAG -programmeur zoals de Xilinx -platformkabel USB.Dit vereist de juiste verbindingen met de JTAG -pinnen: TDI (testgegevens in), TDO (testgegevens uit), TCK (testklok) en TMS (testmodus selecteren).Zorg er ook voor dat de programmapin is aangesloten om herinitialisatie mogelijk te maken.Juiste aarding en VCC -verbindingen zijn belangrijk voor stabiele werking tijdens de configuratie.

4. Programmeer de FPGA: Gebruik van het Xilinx Impact Tool (van de ISE Suite), laad het .bit -bestand naar de FPGA.Als u de JTAG -modus gebruikt, communiceert Impact met de FPGA via de JTAG -interface.Intern omvat het proces het laden van de instructie CFG_IN, het verplaatsen van de bitstream via de Shift-DR-status naar de FPGA via TDI en de configuratie te activeren met de JSTART-instructie.Zodra de bitstream volledig is geladen, gaat de FPGA naar normaal werking.Zorg ervoor dat de uitgevoerde pin hoog wordt, wat een succesvolle configuratie aangeeft.

5. Controleer de configuratie : Na het programmeren is het belangrijk om te bevestigen dat het apparaat de configuratie correct heeft ontvangen.De eenvoudigste cheque is het observeren van de uitgevoerde pin, die hoog moet worden na een succesvolle bitstream -belasting.Bovendien kan de Impact Software een terugtocht- of verificatieproces uitvoeren om de geladen bitstream te vergelijken met het originele bestand, waardoor er tijdens de verzending geen fouten voorkwamen.

XC2S100E-6FTG256C Voordelen

Laag stroomverbruik

De XC2S100E-6FTG256C werkt met een kernspanning van slechts 1,8 V, wat zijn stroomverbruik vermindert in vergelijking met oudere FPGA's die op 2,5 V of hoger werken.Dit maakt het een voorkeurskeuze voor op batterijen bediende of thermisch beperkte systemen, waarbij het beheren van warmte en het uitbreiden van stroomefficiëntie nodig zijn.De lagere spanning verbetert niet alleen de energie -efficiëntie, maar helpt ook bij het minimaliseren van de grootte en kosten van externe stroomregulatiecomponenten.

Hoge I/O -telling

Deze FPGA biedt maximaal 182 I/O -pinnen en biedt een breed scala aan verbindingspunten voor randapparatuur en systeeminterfaces.Met dit hoge pin-telling kan de XC2S100E-6FTG256C complexe signaalroutering en meerdere externe apparaten, zoals geheugeninterfaces, gegevensbussen of communicatiemodules, verwerken.In systemen die veel parallelle verbindingen of gemengde signaalinterfaces vereisen, vermindert dit apparaat de behoefte aan extra multiplexing of externe lijmlogica.

Verbeterde logische bronnen

Met 2.700 logische cellen en een groot aantal configureerbare logische blokken (CLB's) geeft dit apparaat voldoende bronnen voor het bouwen van geavanceerde digitale circuits.Het ondersteunt matige tot complexe ontwerpen, zoals ingebedde controllers, aangepaste gegevenspaden en signaalverwerkingsketens.In vergelijking met eerdere Spartaanse apparaten of CPLD's biedt deze FPGA een merkbare verbetering in logische dichtheid en ontwerpflexibiliteit zonder escalerende kosten.

Geïntegreerd blok ram

De XC2S100E-6FTG256C bevat 40 kbits ingebed blok RAM, waarmee tijdelijke gegevens, buffers of opzoektabellen direct binnen de FPGA kunnen worden opgeroepen.Dit ingebedde geheugen vermindert de behoefte aan externe RAM -chips, waardoor de bom -kosten worden verlaagd en de gegevensdoorvoer verbeteren.Het is handig voor toepassingen zoals data -acquisitie, bufferingsensorinvoer of tijdelijke gegevenscaching tijdens de verwerking.

XC2S100E-6FTG256C verpakkingsafmetingen

• Pakkettype: 256-ball Fine-pitch dunne balrooster array (ftbga)

• Lichaamsgrootte: 17 mm × 17 mm

• Ball -pitch: Meestal 1,0 mm

• Montagetype: Surface Mount

• Pakkethoogte: Ongeveer 1,4 mm

• Vochtgevoeligheidsniveau (MSL): Ja, vochtgevoelig

• Standaardverpakking: Geleverd in laden

XC2S100E-6FTG256C fabrikant

De XC2S100E-6FTG256C wordt vervaardigd door AMDna het verwerven van Xilinx, de oorspronkelijke ontwikkelaar van de Spartan-Iie FPGA-familie.AMD, een wereldwijde leider in high-performance computing en halfgeleidertechnologieën, houdt nu toezicht op de complete portfolio van Xilinx-programmeerbare logische apparaten, waaronder legacy-producten zoals de XC2S100E-6FTG256C.Deze overgang heeft de aanwezigheid van AMD in de FPGA- en Adaptive Computing-markt versterkt, waardoor de voortdurende ondersteuning en integratie van Xilinx's innovatie-erfgoed in AMD's bredere oplossingen op systeemniveau wordt gewaarborgd.Hoewel de XC2S100E-6FTG256C officieel als verouderd is geclassificeerd, blijft AMD levenscyclusondersteuning, technische documentatie en migratiebronnen voor legacy-ontwerpen die rond Spartan-IIE-apparaten zijn gebouwd, vergemakkelijkt.

Conclusie

De XC2S100E-6FTG256C is een krachtige en goedkope FPGA die u 100.000 poorten en 2.700 logische blokken geeft om aangepaste digitale functies te bouwen.Het heeft een ingebouwd geheugen, veel invoer-/uitvoerpennen en loopt snel tot 275 MHz.Het gebruikt slechts 1,8 volt, dus het bespaart stroom.Deze chip is geweldig voor machines in fabrieken, autosystemen, studentenprojecten en het repareren van oude ontwerpen.U kunt ook andere vergelijkbare versies kiezen als u een ander pakket nodig hebt.Hoewel het geen nieuw deel is, werkt het nog steeds goed en wordt het ondersteund door AMD.Het is een slimme pick voor iedereen die digitale systemen bouwt of op het oplossen van digitale systemen.

Datasheet PDF

XC2S100E-6FTG256C datasheets:

Spartan, Virtex, XC17V00 24/APR/2013.PDF

Over ons

ALLELCO LIMITED

Lees verder

Quick Inviry

Stuur een aanvraag, we zullen onmiddellijk reageren.

Veel Gestelde Vragen [FAQ]

1. Hoe verhoudt de XC2S100E-6FTG256C zich tot nieuwere FPGA's zoals Spartan-6 of Artix-7?

In vergelijking met nieuwere families heeft de XC2S100E-6FTG256C minder logische cellen, lagere geheugencapaciteit en langzamere I/O.Het is echter kosteneffectiever voor eenvoudige of matige toepassingen, en het volwassen ontwerp maakt het zeer stabiel en goed gedocumenteerd.

2. Welke programmeerhulpmiddelen heb ik nodig voor het configureren van de XC2S100E-6FTG256C?

U hebt de Xilinx ISE -ontwerpsuite en een compatibele programmeerkabel zoals de Xilinx -platformkabel USB nodig.Met deze tools kunt u de bitstream maken en uploaden via JTAG of andere ondersteunde modi.

3. Kan deze FPGA zowel 3,3 V als 2.5V I/O -signalering verwerken?

Ja, de XC2S100E-6FTG256C ondersteunt een verscheidenheid aan I/O-normen, waaronder LVCMOS en LVTTL, en kan worden geconfigureerd om te werken met zowel 3.3V als 2.5V-signalering via de IOB-instellingen en VREF-ingangen.

4. Wat is het stroomverbruik van de XC2S100E-6FTG256C onder typische belasting?

Onder typische belasting is het kernverbruik vrij laag vanwege de 1,8V kernspanning.Exacte kracht is afhankelijk van de logische activiteit en klokfrequentie, maar het is goed geschikt voor thermisch beperkte systemen.

5. Kunnen meerdere XC2S100E-6FTG256C-apparaten tegelijkertijd worden geprogrammeerd?

Ja, met behulp van de Slave Parallel -modus kunnen meerdere apparaten tegelijkertijd worden geconfigureerd met een gedeelde gegevensbus.Dit versnelt de productietests of systeeminitialisatie in grootschalige toepassingen.

XCS30-3VQ100C FPGA: Functies, programmering en alternatieven

Op 2025/05/7

AD8130AR -versterkingshandleiding: functies, pinout, applicaties en gegevenasheet

Op 2025/05/6

Populaire berichten

-

Complexe instructieset computers: hoe ze de computer hebben gewijzigd?

Op 8000/04/19 147781

-

USB-C-pinout en functies

Op 2000/04/19 112059

-

Met behulp van Xilinx Unified Simulation Primitives: een uitgebreide gids voor FPGA -ontwerp en simulatie

Op 1600/04/19 111352

-

Voedingsspanningen in elektronica: betekenis van VCC, VDD, VEE, VSS en GND

Op 0400/04/19 83813

-

RJ45 -connectorhandleiding: pinout, bedrading, kabeltypen en gebruik

Op 1970/01/1 79627

-

De ultieme gids voor draadkleurcodes in moderne elektrische systemen

De manier waarop onze elektrische systemen kleuren gebruiken, is niet alleen voor uiterlijk.Elke draadkleur geeft nu een specifieke functie aan, waardoor het gemakkelijker wordt om elektrische comp...Op 1970/01/1 66998

-

PURGE VLEP GIDS: Functie, symptomen, testen en vervanging voor optimale motorprestaties

De Purge -klep is een belangrijk onderdeel van het systeem van een auto dat helpt de lucht schoon te houden door brandstofdampen te beheren voordat ze in de atmosfeer kunnen ontsnappen.Dit helpt ni...Op 1970/01/1 63120

-

Kwaliteit (Q) Factor: vergelijkingen en toepassingen

De kwaliteitsfactor, of 'Q', is belangrijk bij het controleren hoe goed inductoren en resonatoren werken in elektronische systemen die radiofrequenties gebruiken (RF).'Q' meet hoe goed een circuit ...Op 1970/01/1 63057

-

Piekprestaties bereiken met de maximale stelling van de stroomoverdracht

De maximale stelling van de stroomoverdracht legt uit hoe energie van een bron, zoals een batterij of generator, naar een aangesloten belasting stroomt.Het toont de exacte voorwaarde waar de belast...Op 1970/01/1 54097

-

A23 Batterijspecificaties en compatibiliteit

De A23-batterij is een kleine, cilindervormige batterij met hoge spanning.Ook wel 23A, 23ae of MN21 genoemd, het loopt op 12 volt en veel hoger dan AA- of AAA -batterijen.Het speciale ontw...Op 1970/01/1 52207