XC2C256-7TQ144C CPLD: PINOUT, FUNCTIES, PROGRAMMING EN GEBRUIKT

In deze handleiding krijg je een duidelijke blik op de XC2C256-7TQ144C, een low-power CPLD van Xilinx's Coolrunner-II-familie (nu AMD).U leert over de PIN-configuratie, CAD-modellen en hoofdfuncties zoals logische capaciteit, I/O-opties, spanningsondersteuning en vermogensbesparende functies.We zullen ook door de architectuur, de I/V -curve en specificaties lopen, gevolgd door applicaties, vergelijkbare onderdelen, programmeerstappen, voor- en nadelen, verpakkingsdetails en informatie over fabrikanten, zodat u precies kunt begrijpen hoe dit apparaat in uw projecten past.Catalogus

Wat is de XC2C256-7TQ144C?

De XC2C256-7TQ144C is een low-power CPLD (complex programmeerbaar logisch apparaat) van Xilinx's Coolrunner-II-familie, nu onderdeel van AMD.Het beschikt over 256 macrocellen en wordt geleverd in een 144-pins TQFP-pakket, ontworpen voor snelle, deterministische werking met minimaal stroomverbruik.Het werkt op een 1,8 V-kern, het biedt betrouwbare prestaties in een compacte vormfactor en is zeer geschikt voor ontwerpen die onmiddellijke mogelijkheden en efficiënte logische implementatie vereisen.Als onderdeel van de veelzijdige Coolrunner-II-serie profiteert het van een bewezen architectuur en brede ontwerpcompatibiliteit.

Op zoek naar XC2C256-7TQ144C?Neem contact met ons op om de huidige voorraad, doorlooptijd en prijzen te controleren.

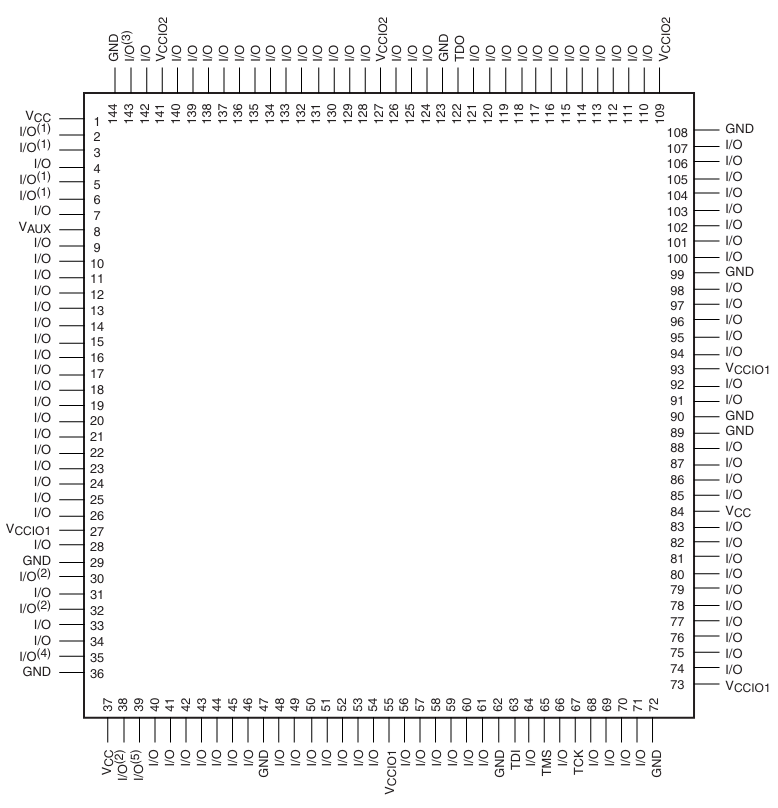

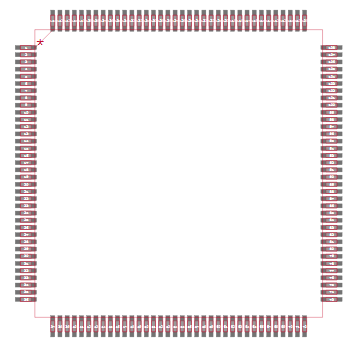

XC2C256-7TQ144C Pin-out diagram

Het XC2C256-7TQ144C PIN-OUT-diagram laat zien hoe de 144 pins zijn gerangschikt voor stroom-, grond-, JTAG- en gebruikersprogrammeerbare I/O-functies.De meeste pinnen zijn I/O, die kunnen worden geconfigureerd als ingangen of uitgangen, en gelijkmatig worden verdeeld om flexibele routing te ondersteunen.VCC-, VCCIO1-, VCCIO2-, VAUX- en GND -pinnen worden rond het pakket geplaatst om een stabiele stroomverdeling en meerdere I/O -spanningsopties te bieden.De JTAG-pennen (TDI, TDO, TMS, TCK) zijn gegroepeerd voor eenvoudig programmeren en testen in het systeem.

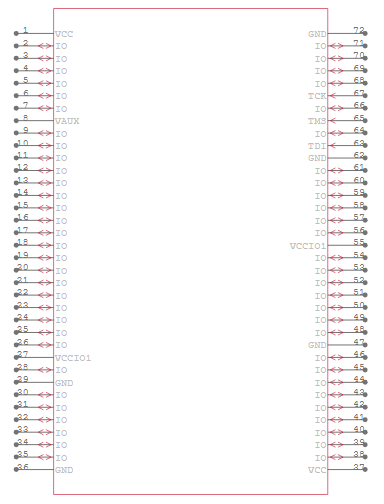

XC2C256-7TQ144C CAD-modellen

XC2C256-7TQ144C Symbool

XC2C256-7TQ144C voetafdruk

XC2C256-7TQ144C 3D-model

XC2C256-7TQ144C-functies

• Apparaattype en familie

De XC2C256-7TQ144C is een complex programmeerbaar logisch apparaat (CPLD) dat behoort tot de Coolrunner-II-familie ontwikkeld door Xilinx (nu AMD).Het is ontworpen voor een laag stroomverbruik met behoud van snelle, deterministische logische prestaties, waardoor het ideaal is voor besturingslogica en interface -toepassingen.

• Logische capaciteit

Dit apparaat bevat 256 macrocellen, de programmeerbare logische bronnen in de CPLD.Deze macrocellen kunnen worden geconfigureerd om verschillende combinatie- en sequentiële logische functies te implementeren, waardoor gematigde capaciteit voor controle, lijmlogica en businterfaces.

• Logische blokken (functieblokken)

Het integreert 16 functieblokken die groepen macrocellen organiseren en beheren.Elk blok biedt lokale interconnect- en producttermbronnen, waardoor flexibele logische implementatie en efficiënte routing binnen het apparaat mogelijk is.

• Gebruiker I/O -pinnen

De XC2C256-7TQ144C biedt maximaal 118 gebruiker-configureerbare I/O-pinnen in zijn TQFP-144-pakket.Met deze hoge pin-telling kan het apparaat tegelijkertijd met meerdere subsystemen communiceren, waardoor het geschikt is voor complexe ontwerpen op bordniveau.

• Kernspanning (VCC)

De kern werkt op een nominale 1,8 V (1,7 V tot 1,9 V -bereik), wat helpt het stroomverbruik te verminderen in vergelijking met oudere 5 V CPLD's.Deze lagere spanning is nuttig in moderne digitale systemen met gemengde spanning.

• Multi-spanning I/O-ondersteuning

De I/O -banken ondersteunen meerdere spanningsstandaarden, waaronder 1,5 V, 1,8 V, 2,5 V en 3,3 V. Met deze flexibiliteit kan de CPLD direct communiceren met componenten die op verschillende spanningsniveaus werken zonder externe niveauverschuivingen.

• High-speed werking

Met een typische pin-to-pins propagatievertraging van ongeveer 5,7 ns (snelheidsgrade "-7") levert het apparaat snelle, deterministische prestaties.Dit maakt het geschikt voor timingkritische toepassingen zoals adres decodering, busarbitrage en controle.

• Laag stroomverbruik

De CoolRunner-II-serie staat bekend om extreem lage standby-stromen, vaak in het microamp-bereik.Met dit lage statische vermogen, gecombineerd met dynamische vermogensbesparende functies, kan de XC2C256-7TQ144C effectief worden gebruikt in batterij-aangedreven of altijd op systemen.

• Datagate -technologie

Deze functie maakt het mogelijk ongebruikte ingangen af te gooien, waardoor onnodig schakelen en het dynamische stroomverbruik worden verminderd.Het is waardevol in toepassingen waarbij bepaalde signalen lange periodes inactief zijn.

• In-system JTAG-programmering

Het apparaat ondersteunt IEEE 1149.1 (JTAG) en IEEE 1532 voor programmering in system.Dit betekent dat de CPLD kan worden geconfigureerd, getest en opnieuw geprogrammeerd zonder het uit het bord te verwijderen, waardoor de ontwikkeling en updates worden vereenvoudigd.

• Geavanceerde klokstructuur

XC2C256-7TQ144C bevat meerdere globale klokken, klokdividers en met dubbele edge geactiveerde registers.Het biedt ook globale set/reset en lokale klokken per macrocell, waardoor flexibele controle wordt gegeven over timing en synchronisatie.

• Schmitt-trigger-ingangen

Geselecteerde invoerpennen kunnen worden geconfigureerd als Schmitt activeert om ruisimmuniteit te verbeteren.Dit is handig voor het verwerken van langzame of lawaaierige ingangssignalen zonder externe conditioneringscircuits toe te voegen.

• Flexibele uitvoerfuncties

De uitgangen ondersteunen drie-staten bediening, Slew Rate Control, Bus-Hold, Open-Drain-configuraties en optionele pull-ups.Deze opties maken het gemakkelijk om de CPLD aan te passen aan verschillende busnormen en externe belastingomstandigheden.

• Advanced Interconnect Matrix (AIM)

Een geavanceerde interconnectmatrix koppelt functieblokken efficiënt en biedt volledige productie-routering op het apparaat.Dit verbetert de flexibiliteit van de logische plaatsing en helpt bij het handhaven van voorspelbare timingprestaties.

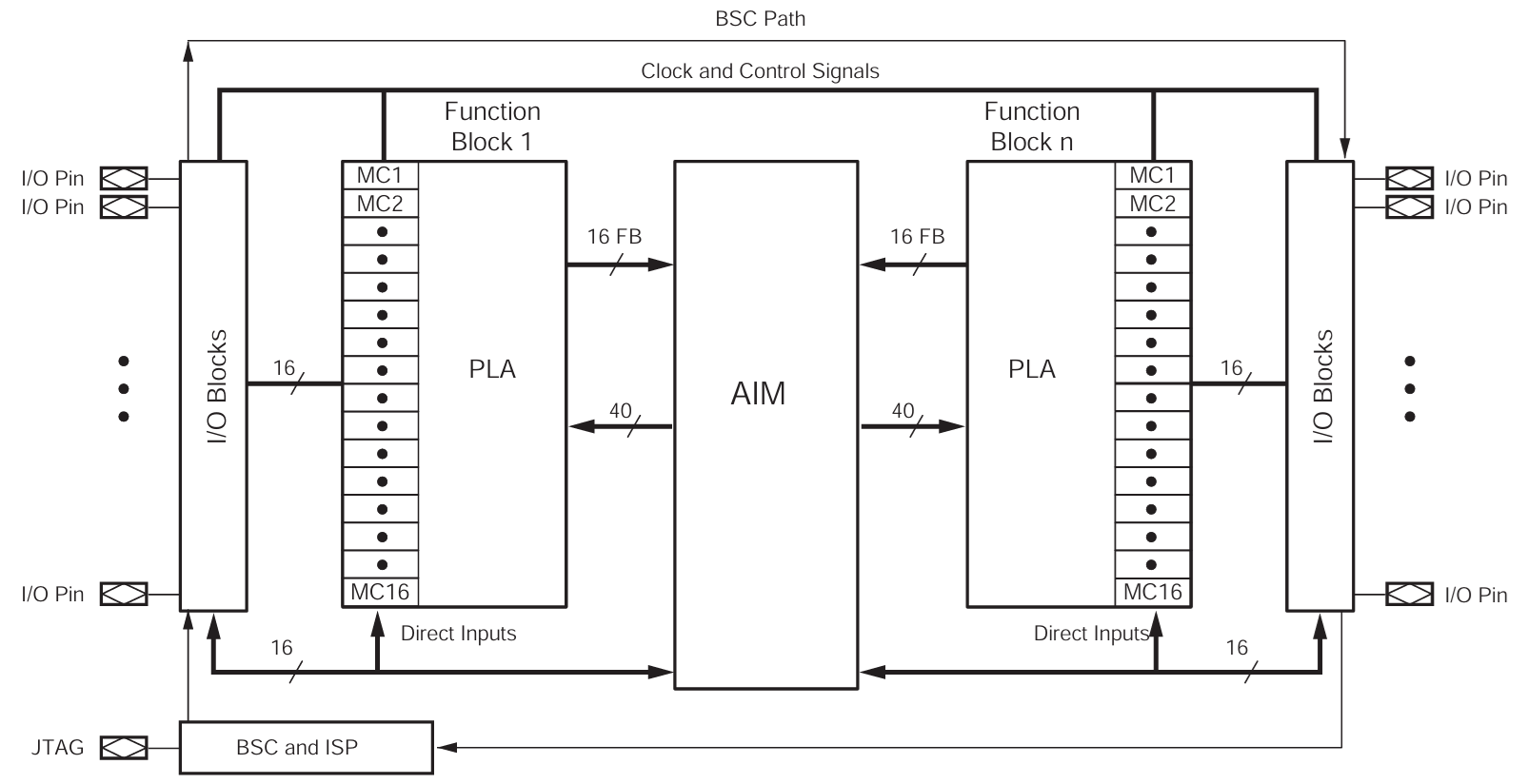

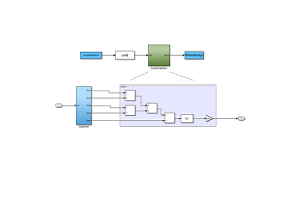

CoolRunner-II CPLD-architectuur

De CoolRunner-II CPLD-architectuur van de XC2C256-7TQ144C is gebouwd rond functieblokken, I/O-blokken en een geavanceerde interconnectmatrix (AIM).Elk functieblok bevat macrocellen en een programmeerbare logische array (PLA) die door de gebruiker gedefinieerde logica implementeren, terwijl het AIM-routes signalen tussen blokken efficiënt routes.De I/O-blokken interface met de interne logica met externe pinnen en speciale JTAG en BSC/ISP-circuitondersteuning ondersteunen in-system programmering en testen.Deze gestructureerde en onderling verbonden architectuur maakt snelle, deterministische prestaties mogelijk met een laag stroomverbruik, waardoor het ideaal is voor controle-, interface- en lijmlogica in digitale systemen.

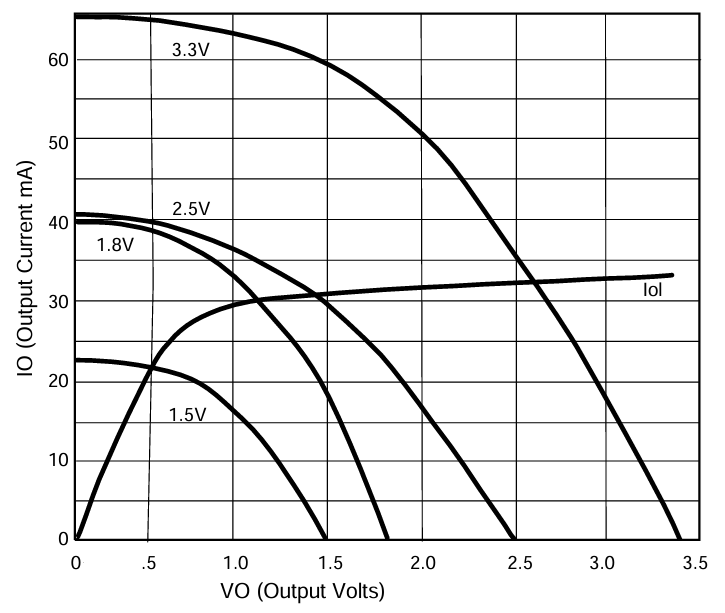

Typische I/V -curve voor XC2C256

De typische I/V-curve voor de XC2C256-7TQ144C illustreert de relatie tussen uitgangsspanning (VO) en uitgangsstroom (IO) voor verschillende I/O-voedingsspanningen (1,5 V, 1,8 V, 2,5 V en 3,3 V).Naarmate de voedingsspanning toeneemt, kan het apparaat hogere stromen branden of zinken voordat de uitgangsspanning aanzienlijk begint te dalen.Dit gedrag is belangrijk voor het begrijpen van de aandrijfmogelijkheden van de CPLD bij het interfaceren met externe componenten, waardoor signaalniveaus geldig blijven onder belasting.Velen gebruiken deze curve om de juiste I/O-spanningen te selecteren en een betrouwbare werking te garanderen in toepassingen die specifieke stroomsterkten van stroomaanvallen vereisen.

XC2C256-7TQ144C specificaties

|

Type |

Parameter |

|

Fabrikant |

AMD/Xilinx |

|

Serie |

Coolrunner II |

|

Verpakking |

Dienblad |

|

Onderdeelstatus |

Verouderd |

|

Programmeerbaar type |

In systeem programmeerbaar |

|

Vertragingstijd TPD (1) Max |

6.7 NS |

|

Spanningstoevoer - Intern |

1.7 V ~ 1.9 V |

|

Aantal logische elementen/blokken |

16 |

|

Aantal macrocellen |

256 |

|

Aantal poorten |

6000 |

|

Aantal I/O |

118 |

|

Bedrijfstemperatuur |

0 ° C ~ 70 ° C (TA) |

|

Montagetype |

Oppervlaktemontage |

|

Pakket / kast |

144-lqfp

|

|

Leverancierapparaatpakket |

144-tqfp (20 × 20) |

|

Base Productnummer |

XC2C256 |

XC2C256-7TQ144C-toepassingen

1. Lijmlogica en interface overbruggen

De XC2C256-7TQ144C is ideaal voor het implementeren van lijmlogica, die signalen verbindt en coördineert tussen verschillende digitale componenten.Het kan functies zoals adres decodering, busarbitrage en protocolvertaling aan, waardoor een soepele communicatie tussen microcontrollers, geheugen, sensoren en andere randapparatuur mogelijk is.De voorspelbare timing en snelle pin-to-pins vertragingen zorgen voor betrouwbare interface, zelfs in complexe bordontwerpen.

2. Low-power en battery-operated apparaten

Dankzij zijn Fast Zero Power (FZP) -technologie en zeer lage standby-stroom, is deze CPLD zeer geschikt voor draagbare en op batterijen aangedreven elektronica.Het kan continu worden aangedreven terwijl het minimale energie consumeert, waardoor het perfect is voor altijd controle of bewakingscircuits.U kunt het stroomverbruik verder verminderen met functies zoals datagate, die dynamisch schakelen minimaliseert wanneer ingangen inactief zijn.

3. Controlelogica en sequencing

Het apparaat blinkt uit in het implementeren van eindige statusmachines, timingcontrole en signaalsequencing die nodig is in veel ingebedde systemen.Door de deterministische, niet-vluchtige architectuur kan de besturingslogica onmiddellijk na de power-up actief worden zonder configuratievertragingen.Dit maakt het een sterke keuze voor reset-logica, handshaking-circuits en andere tijdkritische controletaken.

4. Geïmbedded systeemondersteuning en perifere logica

In ingebedde ontwerpen kan de XC2C256-7TQ144C fungeren als een aanpasbare ondersteuningschip, het implementeren van gespecialiseerde interfaces of het uitbreiden van de mogelijkheden van een microcontroller.Het kan omgaan met communicatieprotocollen zoals SPI, I²C of UART, chip -selecties genereren of interruptroutering beheren.Door deze functies van de CPU te laden, vereenvoudigt het de ontwikkeling van firmware en verbetert het de algehele systeemprestaties.

XC2C256-7TQ144C vergelijkbare onderdelen

|

Specificatie |

XC2C256-7TQ144C |

XC2C256-7TQ144I |

XC2C256-7TQG144I |

XC2C256-7VQ100C |

XC2C256-7VQG100C |

XC2C256-6TQ144C |

|

Apparaatfamilie |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

|

Logische dichtheid (macrocells) |

256 |

256 |

256 |

256 |

256 |

256 |

|

Pakkettype |

TQFP-144 |

TQFP-144 |

TQFP-144 (PB-vrij) |

VQFP-100 |

VQFP-100 (PB-vrij) |

TQFP-144 |

|

Snelheidsgraad |

-7 |

-7 |

-7 |

-7 |

-7 |

-6 (sneller) |

|

Temperatuurbereik |

Commercial (0 - 70 ° C) |

Industrieel (-40-85 ° C) |

Industrieel (-40-85 ° C) |

Commercial (0 - 70 ° C) |

Commercial (0 - 70 ° C) |

Commercial (0 - 70 ° C) |

|

I/O PIN -telling |

118 |

118 |

118 |

80 |

80 |

118 |

|

Kernspanning (VCC) |

1.8 V |

1.8 V |

1.8 V |

1.8 V |

1.8 V |

1.8 V |

|

I/O -spanningsondersteuning |

1.5 V - 3.3 V |

1.5 V - 3.3 V |

1.5 V - 3.3 V |

1.5 V - 3.3 V |

1.5 V - 3.3 V |

1.5 V - 3.3 V |

|

Naleving / PB-vrij |

Standaard |

Standaard |

PB-vrij / ROHS |

Standaard |

PB-vrij / ROHS |

Standaard |

|

Verschillen |

Baseline commerciële versie |

Industriële temp -versie |

Industrieel + PB-vrije versie |

Kleiner pakket, minder I/O |

PB-vrije kleinere versie |

Snellere timingversie |

XC2C256-7TQ144C programmeerstappen

Het programmeren van de XC2C256-7TQ144C is een eenvoudig proces waarbij uw ontwerp wordt voorbereid, het programmeerbestand genereert en het via JTAG in de CPLD laadt.Door elke stap zorgvuldig te volgen, kunt u zorgen voor een succesvolle configuratie en de juiste apparaatbewerking op uw bord.

1. Ontwerp en synthetiseren

U begint met het schrijven van uw logische ontwerp met behulp van HDL (VHDL of Verilog) of schematische invoer.Na het voltooien van het ontwerp voert u het syntheseproces uit, dat uw logica omzet in de interne structuur van macrocellen en interconnects van het apparaat.Deze stap zorgt ervoor dat uw ontwerp compatibel is met de XC2C256 -architectuur en klaar voor implementatie.

2. Plaats en route / implementatie (passen)

Vervolgens voert u plaats en route uit, ook bekend als fitting, die uw gesynthetiseerde logica toewijst aan werkelijke fysieke macrocellen en routeringsbronnen in de CPLD.De tool controleert de timingbeperkingen, lost het gebruik van middelen op en optimaliseert paden om te voldoen aan de prestaties van uw ontwerp.Dit zorgt ervoor dat het circuit betrouwbaar zal worden uitgevoerd zodra ze in het apparaat zijn geprogrammeerd.

3. Genereer programmeerbestand

Nadat de implementatie is voltooid, genereert u het programmeerbestand (bit-, jam- of SVF -indeling) dat de exacte configuratiegegevens voor het apparaat bevat.Dit bestand geeft aan hoe elke macrocell, interconnect en I/O is ingesteld om uw logica te implementeren.Als u dit bestand klaar hebt, is nodig voordat u doorgaat naar de werkelijke programmering van het apparaat.

4. JTAG / In-system programmeren

Ten slotte sluit u het apparaat aan op uw pc met behulp van een JTAG -programmeerkabel en opent u het Xilinx -impactgereedschap (of gelijkwaardig).Vervolgens laadt u het gegenereerde programmeerbestand en downloadt het naar de XC2C256-7TQ144C via de JTAG-pinnen (TDI, TDO, TCK, TMS).Zodra het proces is voltooid, begint de CPLD onmiddellijk te werken met uw geprogrammeerde logica, zonder een stroomcyclus of extern configuratiegeheugen te vereisen.

XC2C256-7TQ144C Voordelen en nadelen

Voordelen

• Zeer laag standby-vermogen, ideaal voor ontwerpen op batterijen.

• Directe bewerking zonder configuratievertraging.

• Voorspelbare timing voor gemakkelijkere ontwerpafsluiting.

• Vervangt meerdere discrete logische chips, bespaar ruimte en kosten.

• Ondersteunt meerdere I/O -spanningen zonder externe niveauverschuivingen.

Nadelen

• Beperkte logische capaciteit vergeleken met grotere CPLD's of FPGA's.

• Geen ingebouwde DSP, RAM- of hogesnelheidszaken.

• Verouderd raken, waardoor toekomstige inkoop harder wordt.

• Lagere prestatieplafond voor hogesnelheidstoepassingen.

• Minder routeringsflexibiliteit voor complexe of onregelmatige ontwerpen.

XC2C256-7TQ144C verpakkingsafmetingen

|

Type |

Parameter |

|

Pakkettype |

TQFP-144 |

|

Pakket lichaamsgrootte |

20 mm × 20 mm |

|

Hoofdlichaam |

0,5 mm |

|

Aantal pinnen |

144 |

|

Pakkethoogte (max) |

1,4 mm |

|

Pakketdikte (nominaal) |

1,0 mm |

|

Loodlengte |

0,45 mm ~ 0,75 mm |

|

Loodbreedte |

0,17 mm ~ 0,27 mm |

|

Montagetype |

Oppervlaktemontage |

|

Leverancierapparaatpakket |

144-tqfp (20 × 20) |

XC2C256-7TQ144C fabrikant

De XC2C256-7TQ144C wordt vervaardigd door Xilinx, een toonaangevend bedrijf in programmeerbare logische oplossingen.Xilinx wordt algemeen erkend voor baanbrekende FPGA- en CPLD-technologieën en biedt betrouwbare en krachtige apparaten voor industriële, commerciële en consumententoepassingen.Tegenwoordig werkt Xilinx als onderdeel van AMD, blijven geavanceerde programmeerbare logische producten leveren met sterke ondersteuning en innovatie op lange termijn.

Conclusie

De XC2C256-7TQ144C valt op voor zijn lage stroomverbruik, snelle deterministische prestaties en multi-spannings-I/O-flexibiliteit, waardoor het een betrouwbare keuze is voor moderne digitale ontwerpen.De uitgebalanceerde combinatie van 256 macrocellen, 118 I/O -pins en geavanceerde interconnect -architectuur ondersteunt een breed scala aan controle-, interface- en lijmlogica -functies.Met ondersteuning voor in-system programmering, datagate power-saving-functies en robuuste I/O-configuraties, integreert het soepel in ingebedde systemen en omgevingen met gemengde spanning.

Datasheet PDF

XC2C256-7TQ144C datasheets:

Over ons

ALLELCO LIMITED

Lees verder

Quick Inviry

Stuur een aanvraag, we zullen onmiddellijk reageren.

Veel Gestelde Vragen [FAQ]

1. Vereist de XC2C256-7TQ144C een extern configuratiegeheugen?

Nee. Een van de voordelen is onmiddellijke operatie.De configuratie wordt intern opgeslagen, dus deze wordt klaar voor uitgevoerd zonder een extern prom- of flash -geheugen.

2. Welke programmeerhulpmiddelen zijn compatibel met XC2C256-7TQ144C?

U kunt het apparaat programmeren met behulp van Xilinx Impact -software met een JTAG -programmeerkabel.Velen gebruiken ook compatibele JTAG-programmeurs van derden, maar zorg ervoor dat ze IEEE 1149.1/1532-normen ondersteunen.

3. Kan de XC2C256-7TQ144C meerdere discrete logische IC's in uw ontwerp vervangen?

Ja.Met zijn 256 macrocellen en flexibele I/O kan deze CPLD verschillende lijmlogica en besturingsfuncties integreren in één apparaat, waardoor u de bordruimte en het aantal componenten kunt verminderen.

4. Is de XC2C256-7TQ144C geschikt voor batterijtoepassingen met een laag vermogen?

Ja.Dankzij zijn Fast Zero Power (FZP) -technologie en een zeer lage standby-stroomstroom, is het ideaal voor altijd op circuits, draagbare apparaten en vermogensgevoelige ingebedde systemen.

5. Kun je de XC2C256-7TQ144C gebruiken voor snelle signaalverwerking?

Het is niet ontworpen voor hoogsnelheid DSP of transceiver-taken.Hoewel het snelle pin-to-pins vertragingen levert, is het het meest geschikt voor controle-, interface- en timinglogica, niet voor complexe gegevensverwerking.

EP2S60F672C4 FPGA: Functies, Applicaties, Programming & Datasheet Guide

Op 2025/10/4

EPM3256AFC256-7 CPLD-overzicht: Functies, Pinout, programmeren en applicaties

Op 2025/10/3

Populaire berichten

-

Complexe instructieset computers: hoe ze de computer hebben gewijzigd?

Op 8000/04/18 147776

-

USB-C-pinout en functies

Op 2000/04/18 112018

-

Met behulp van Xilinx Unified Simulation Primitives: een uitgebreide gids voor FPGA -ontwerp en simulatie

Op 1600/04/18 111351

-

Voedingsspanningen in elektronica: betekenis van VCC, VDD, VEE, VSS en GND

Op 0400/04/18 83777

-

RJ45 -connectorhandleiding: pinout, bedrading, kabeltypen en gebruik

Op 1970/01/1 79575

-

De ultieme gids voor draadkleurcodes in moderne elektrische systemen

De manier waarop onze elektrische systemen kleuren gebruiken, is niet alleen voor uiterlijk.Elke draadkleur geeft nu een specifieke functie aan, waardoor het gemakkelijker wordt om elektrische comp...Op 1970/01/1 66964

-

PURGE VLEP GIDS: Functie, symptomen, testen en vervanging voor optimale motorprestaties

De Purge -klep is een belangrijk onderdeel van het systeem van een auto dat helpt de lucht schoon te houden door brandstofdampen te beheren voordat ze in de atmosfeer kunnen ontsnappen.Dit helpt ni...Op 1970/01/1 63104

-

Kwaliteit (Q) Factor: vergelijkingen en toepassingen

De kwaliteitsfactor, of 'Q', is belangrijk bij het controleren hoe goed inductoren en resonatoren werken in elektronische systemen die radiofrequenties gebruiken (RF).'Q' meet hoe goed een circuit ...Op 1970/01/1 63041

-

Piekprestaties bereiken met de maximale stelling van de stroomoverdracht

De maximale stelling van de stroomoverdracht legt uit hoe energie van een bron, zoals een batterij of generator, naar een aangesloten belasting stroomt.Het toont de exacte voorwaarde waar de belast...Op 1970/01/1 54097

-

A23 Batterijspecificaties en compatibiliteit

De A23-batterij is een kleine, cilindervormige batterij met hoge spanning.Ook wel 23A, 23ae of MN21 genoemd, het loopt op 12 volt en veel hoger dan AA- of AAA -batterijen.Het speciale ontw...Op 1970/01/1 52189