EP2S60F672C4 FPGA: Functies, Applicaties, Programming & Datasheet Guide

In deze gids krijg je een duidelijk overzicht van de EP2S60F672C4, een krachtige FPGA uit de familie Stratix II van Intel.U leert over de belangrijkste functies, architectuur, blokstructuur en technische specificaties om te begrijpen hoe het past in geavanceerde digitale ontwerpen.Het leidt u ook door zijn programmeerstappen, toepassingen, voor- en nadelen, zodat u precies kunt zien waar en hoe dit apparaat kan worden gebruikt.Catalogus

Wat is de EP2S60F672C4?

De EP2S60F672C4 is een FPGA met hoge dichtheid van Intel (voorheen Altera), behorend tot de Stratix II-familie.Gebouwd op een 90 nm, 1,2 V koper SRAM-proces, levert het een aanzienlijke logische capaciteit binnen een FBGA-pakket van 672-ball, waardoor het ideaal is voor complexe digitale systemen.Als onderdeel van de EP2S-serie bevindt het "60" -apparaat zich in het midden-tot-upper bereik van de Stratix II-opstelling, die een sterke balans van logische dichtheid, ingebed geheugen en I/O-bronnen biedt.Bekend om zijn robuuste architectuur en betrouwbaarheid, blijft deze FPGA een vertrouwde keuze in veel geavanceerde ontwerpen.

Op zoek naar EP2S60F672C4?Neem contact met ons op om de huidige voorraad, doorlooptijd en prijzen te controleren.

EP2S60F672C4 CAD -modellen

EP2S60F672C4 -symbool

Ep2S60F672C4 voetafdruk

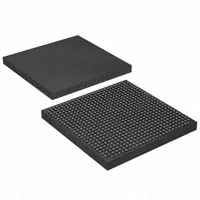

EP2S60F672C4 3D -model

EP2S60F672C4 Functies

• Geavanceerd 90 nm, 1,2 V CMOS -proces

EP2S60F672C4 is gefabriceerd op een 90 nm COPER CMOS-proces van al-laags COMO's dat wordt uitgevoerd op een kernspanning van 1,2 V.Deze technologie maakt een hoge snelheid, verminderd stroomverbruik en een grotere logische dichtheid mogelijk in vergelijking met oudere FPGA -generaties.

• Adaptive Logic Module (ALM) architectuur

Het apparaat gebruikt aalmoes als de logische bouwsteen in plaats van traditionele logische elementen.Deze architectuur verbetert het gebruik van hulpbronnen, waardoor complexere logische functies efficiënt kunnen worden geïmplementeerd binnen hetzelfde siliciumgebied.

• Hoge logische dichtheid

Met ongeveer 60.440 logische elementen (24.176 aalmoes) ondersteunt de FPGA grote en geavanceerde digitale ontwerpen.Deze hoge capaciteit maakt het geschikt voor toepassingen zoals signaalverwerking, communicatie en ingebedde besturingssystemen.

• Trimatrix ™ on-chip geheugen

EP2S60F672C4 integreert drie soorten RAM-blokken, (M512, M4K en M-RAM) om in totaal ongeveer 2,4 MBits aan ingesloten geheugen te bieden.Met deze mix kunnen kleine FIFO's, middelgrote buffers en grote herinneringen met dubbele poorten efficiënt worden geïmplementeerd.

• Speciale DSP -blokken

Het apparaat bevat 36 speciale DSP -blokken die zijn ontworpen voor rekenkundige bewerkingen zoals vermenigvuldigingen, accumulaties en FIR -filtering.Deze blokken stimuleren de prestaties in berekeningsintensieve taken terwijl algemene logische bronnen worden opgeslagen.

• High-speed I/O en signaalintegriteit

Het ondersteunt verschillende single-end en differentiële I/O-normen samen met dynamische fase-uitlijning (DPA) circuits.Deze functies maken stabiele, snelle gegevensoverdracht tot 1 Gbps mogelijk, waardoor betrouwbare communicatie met externe componenten wordt gewaarborgd.

• Rijke externe geheugeninterface -ondersteuning

De FPGA is compatibel met DDR, DDR2, QDR II, RLDRAM II en andere geheugenstandaarden.Ingebouwde interface-ondersteuning vereenvoudigt het ontwerp van het bord en bereikt hoge gegevensdoorvoer voor geheugenintensieve toepassingen.

• Flexibel klokbeheer

Maximaal 12 on-chip PLL's maken klokvermenigvuldiging, deling, faseverschuiving en glitch-vrije omschakeling mogelijk.U kunt klokdomeinen verfijnen en jitter verminderen, ter ondersteuning van interne klokfrequenties van maximaal 500-550 MHz.

• Bitstream -codering en herconfiguratie

EP2S60F672C4 ondersteunt op AES gebaseerde bitstream-codering om intellectueel eigendom te beveiligen.Het biedt ook op externe herconfiguratie mogelijkheden, waardoor updates in het veld kunnen worden ingeschakeld zonder het apparaat te vervangen.

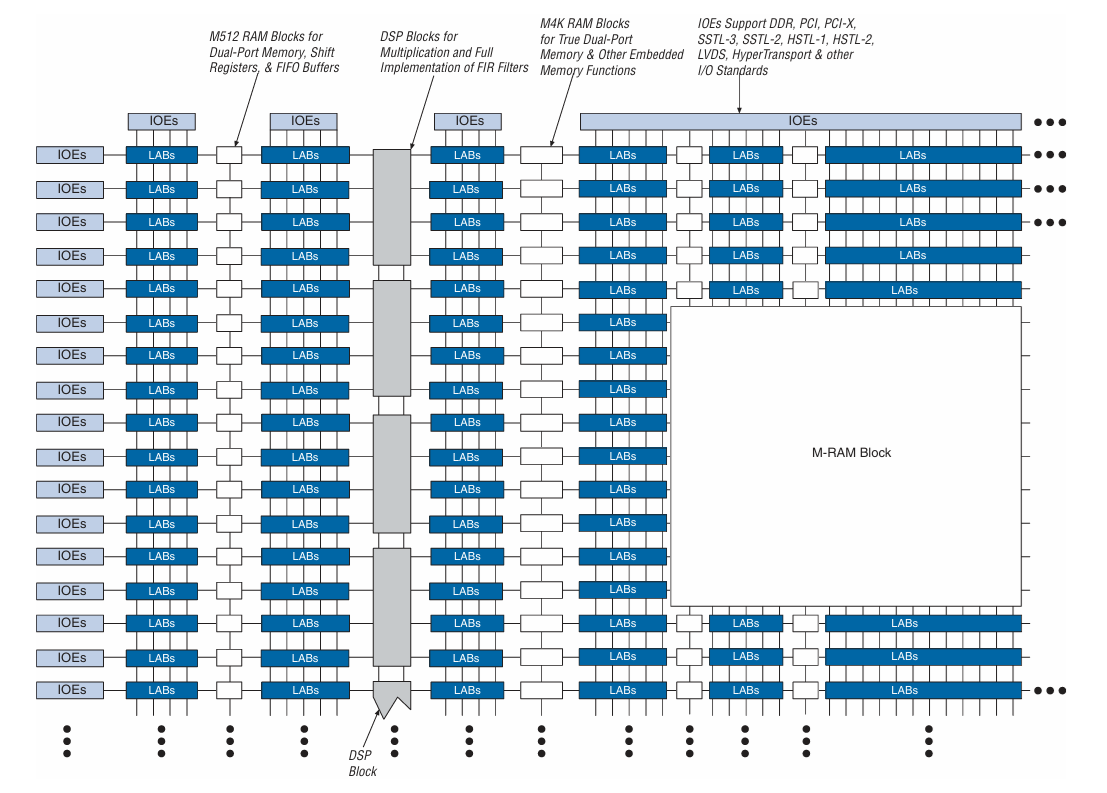

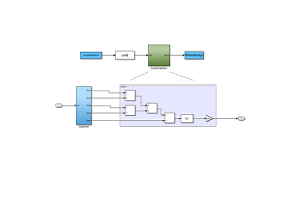

Stratix II blokdiagram

Het Stratix II -blokdiagram, zoals weergegeven voor EP2S60F672C4, illustreert de interne opstelling van logica-, geheugen- en DSP -bronnen die de kern van de FPGA vormen.Logische arrayblokken (laboratoria) zijn gerangschikt in een normaal rooster, omgeven door ingebedde RAM- en DSP-kolommen, die snel rekenkundige en on-chip opslagmogelijkheden bieden.Perifere I/O -elementen en kloknetwerken omlijsten deze structuur, waardoor efficiënte gegevensoverdracht en timingregeling tussen de FPGA- en externe apparaten mogelijk wordt.Dit diagram is belangrijk omdat het helpt te begrijpen hoe verschillende functionele blokken fysiek zijn georganiseerd, waardoor ze plaatsing, routing en algemene systeemprestaties kunnen optimaliseren.

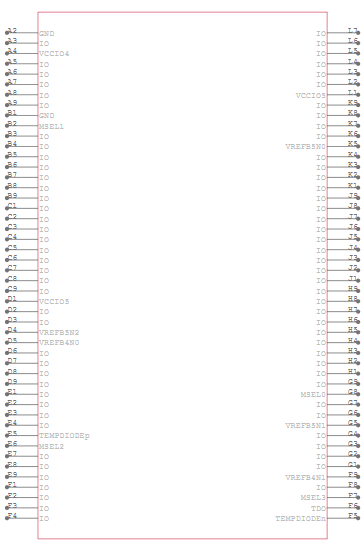

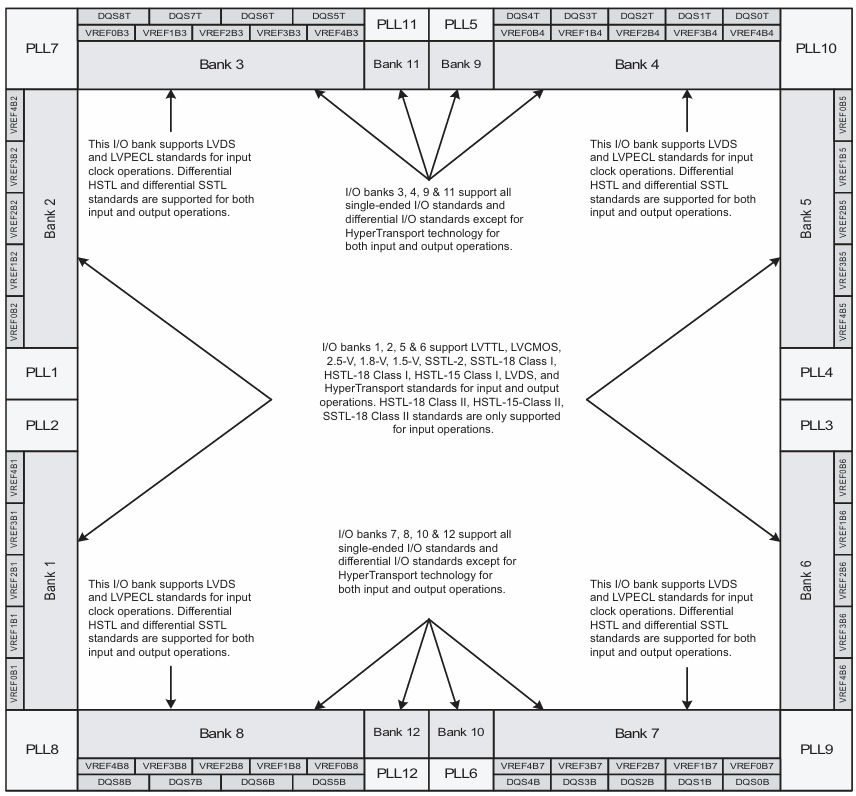

Stratix II I/O Banks -diagram

Dit Stratix II I/O -bankendiagram illustreert hoe de invoer-/uitgangspinnen van de EP2S60F672C4 zijn gegroepeerd en welke elektrische normen elke groep ondersteunt.Elke I/O -bank is ontworpen om specifieke spanningsniveaus, signaleringstypen en functies zoals LVTTL-, SSTL-, LVDS- of klokinvoerstandaarden aan te kunnen.De lay-out laat zien hoe verschillende banken (bijv. 1, 2, 5, 6 versus 3, 4, 7, 8, enz.) Zijn geoptimaliseerd voor ofwel algemene I/O- of hogesnelheidsdifferentiële signalering, inclusief ondersteuning voor LVD's/LVPecl-klokinvoer aan de randen.Het begrijpen van deze structuur is belangrijk bij het toewijzen van pins, omdat de juiste bankselectie zorgt voor elektrische compatibiliteit, bordroutering vereenvoudigt en de prestaties van de FPGA in high-speed ontwerpen maximaliseert.

EP2S60F672C4 -specificaties

|

Type |

Parameter |

|

Fabrikant |

Altera/intel |

|

Serie |

Stratix® II |

|

Verpakking |

Dienblad |

|

Onderdeelstatus |

Verouderd |

|

Aantal laboratorium/CLB's |

3022 |

|

Aantal logische elementen/cellen |

60,440 |

|

Totaal rambits |

2.544,192 |

|

Aantal I/O |

492 |

|

Spanning - levering |

1.15 V ~ 1,25 V |

|

Montagetype |

Oppervlaktemontage |

|

Bedrijfstemperatuur |

0 ° C ~ 85 ° C (TJ) |

|

Pakket / kast |

672-BBGA |

|

Leverancierapparaatpakket |

672-FBGA (27 × 27) |

|

Base Productnummer |

EP2S60 |

EP2S60F672C4 -toepassingen

1. Digitale signaalverwerking (DSP) en filteren

EP2S60F672C4 is zeer geschikt voor het implementeren van krachtige DSP-functies zoals FIR- en IIR-filters, FFT-verwerking en complexe rekenkundige bewerkingen.De speciale DSP -blokken verwerken efficiënt vermenigvuldigingen en accumulaties, waardoor algemene logische bronnen worden vrijgemaakt voor andere taken.Het on-chip trimatrix ™ -geheugen maakt soepele gegevensbuffering en pipelining mogelijk, wat geweldig is voor realtime verwerking bij hoge steekproefsnelheden.Dit maakt het apparaat ideaal voor geavanceerde audio-, video- en radarsignaaltoepassingen.

2. Snelle communicatie en netwerken

De snelle I/O-interfaces en dynamische fase-uitlijning (DPA) van de FPGA ondersteunen betrouwbare, gigabit-niveau data-transmissie.Het kan communicatieprotocollen en fysieke laagfuncties implementeren voor systemen zoals routers, schakelaars en backplane -verbindingen.Met zijn grote logische capaciteit en flexibele PLL's kan het complexe timing- en protocolconversies tussen meerdere hogesnelheidsinterfaces beheren.Deze mogelijkheden maken het sterk geschikt voor telecominfrastructuur en netwerkapparatuur met hoge bandbreedte.

3. Geheugencontrollers en gegevensverwerkingssystemen

EP2S60F672C4 ondersteunt verschillende externe geheugeninterfaces, waaronder DDR, DDR2, RLDRAM II en QDR II, waardoor het ideaal is voor het ontwerpen van geheugencontrollers met hoge bandbreedte.Het kan omgaan met gegevensbuffering, het genereren van adres en arbitrage bij hoge snelheden met minimale latentie.De combinatie van snelle kloknetwerken en ingebedde RAM -blokken maakt een efficiënt beheer van grote gegevensstromen mogelijk.Dit maakt de FPGA geschikt voor beeldverwerking, videostreaming en wetenschappelijke berekeningsplatforms die afhankelijk zijn van zware gegevensdoorvoer.

4. Aangepaste logica en ingebedde versnelling

Met meer dan 60.000 logica -elementen en rijk klokbeheer kan de FPGA aangepaste hardware -versnellers hosten voor specifieke algoritmen.Ontwerpers gebruiken het vaak om computationeel intensieve taken van CPU's te laden, zoals codering, protocol parsing of realtime controlelussen.Het kan ook meerdere functionele blokken integreren, waardoor het geschikt is voor complexe SOC-achtige ontwerpen.Deze flexibiliteit maakt het waardevol in applicaties zoals industriële automatisering, beveiligingssystemen en ruimtevaartbesturingseenheden.

5. Platforms voor prototyping en educatieve ontwikkeling

Het EP2S60 -apparaat wordt vaak aangetroffen op FPGA -ontwikkelingskits die worden gebruikt voor prototyping, testen en academisch onderzoek.De balans tussen logische capaciteit, I/O -telling en DSP -mogelijkheden stelt ingenieurs en studenten in staat om volledige systemen op één chip te implementeren en te verifiëren.Het ondersteunt een snelle iteratie van digitale ontwerpen, waardoor hardware -verificatie mogelijk is voordat ze zich inzetten voor ASIC -ontwikkeling.Veel universiteiten en R & D -laboratoria gebruiken het om geavanceerde digitale ontwerp- en signaalverwerkingsconcepten te onderwijzen.

EP2S60F672C4 vergelijkbare onderdelen

|

Specificatie |

EP2S60F672C4 |

EP2S60F672C3N |

EP2S60F672C5 |

EP2S60F672C5N |

EP2S60F672I4

|

EP2S60F672I3N |

|

Familie / serie |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

|

Logica -elementen (LE) |

60,440 |

60,440 |

60,440 |

60,440 |

60,440 |

60,440 |

|

Aalmoes |

24,176 |

24,176 |

24,176 |

24,176 |

24,176 |

24,176 |

|

Pakket |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

|

Snelheidsgraad |

C4 (STD) |

C3 (sneller) |

C5 (sneller) |

C5 (sneller) |

I4 (std) |

I3 (sneller) |

|

Temperatuurcijfer |

Commercial (0 ~ 70 ° C) |

Commercieel |

Commercieel |

Commercieel |

Industrieel (−40 ~ 100 ° C) |

Industrieel (−40 ~ 100 ° C) |

|

I/O -pinnen |

492 |

492 |

492 |

492 |

492 |

492 |

|

On-chip geheugen |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

|

Kernspanning |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

|

Hoofdverschil |

Baseline commerciële snelheid |

C3 Speed Bin, loodvrij "N" |

Bin met een hogere snelheid |

Bin met een hogere snelheid, "N" variant |

Industriële temperatuur, dezelfde dichtheid |

Industrieel, snellere snelheid, loodvrij |

Ep2S60F672C4 programmeerstappen

Voordat u de EP2S60F672C4 FPGA in uw ontwerp kunt gebruiken, moet u deze correct configureren met uw gecompileerde bitstream.Dit proces omvat het voorbereiden van het programmeerbestand, het instellen van de hardware-interface en ervoor zorgen dat de configuratie correct wordt geladen bij aan / uit-up.

Stap 1: Maak en compileer uw ontwerp

U begint met het ontwikkelen van uw logische ontwerp met behulp van Intel Quartus II -software.Na het voltooien van het ontwerp compileert u het om het programmeerbestand (.sof of .pof) specifiek voor het EP2S60F672C4 -apparaat te genereren.Het compilatieproces controleert op timing, pin -toewijzingen en gebruiksgebruik om ervoor te zorgen dat uw ontwerp binnen de architectuur van de FPGA past.Eenmaal gecompileerd, is uw bitstream klaar voor apparaatconfiguratie.

Stap 2: Stel de programmeerhardware in

Vervolgens bereidt u de fysieke programmeerinterface tussen uw pc en het FPGA -bord voor.Meestal houdt dit in dat het een USB-blaster of compatibele JTAG-kabel aansluit op de JTAG-poort van het apparaat.U moet verifiëren dat Quartus II de programmeur herkent en dat het doelapparaat correct is gedetecteerd.Deze stap zorgt voor stabiele communicatie voordat het configuratieproces wordt gestart.

Stap 3: Laad het programmeerbestand in het apparaat

Met behulp van de Quartus II Programmer -tool voegt u het gecompileerde .sof- of .pof -bestand toe en selecteert u de EP2S60F672C4 in de lijst met gedetecteerde apparaten.Vervolgens initiëren u de programmeersequentie, waarbij de bitstream wordt overgebracht en in de SRAM -configuratiecellen van de FPGA wordt geladen.U moet de voortgangsbalk en statusberichten controleren om een succesvolle configuratie te bevestigen.Eenmaal voltooid, begint de FPGA onmiddellijk de geprogrammeerde logica uit te voeren.

Stap 4: Controleer de configuratie en bewerking

Na het programmeren controleert u dat het apparaat functioneert zoals bedoeld.Quartus II biedt een verificatieoptie om de configuratie CRC en statussignalen te controleren, zodat het ontwerp correct is geladen.U kunt ook uw I/O -functies testen of een functionele simulatie uitvoeren om systeemgedrag te bevestigen.Deze laatste stap zorgt ervoor dat uw ontwerp volledig operationeel en stabiel is op de hardware.

EP2S60F672C4 -voor- en nadelen

Voordelen

• Hoge logische dichtheid voor complexe ontwerpen

• Goede prestatie-to-cost-verhouding

• Gemakkelijke migratie binnen dezelfde familie

• Stabiele en volwassen ontwikkelingstools

• Bewezen betrouwbaarheid bij industrieel gebruik

Nadelen

• Verouderd en moeilijker te betrekken

• Hoger stroomverbruik dan nieuwere FPGA's

• Geen moderne high-speed transceivers

• Meer moeilijke timingafsluiting bij een hoog gebruik

• Beperkte schaalbaarheid voor toekomstige protocollen

Ep2S60F672C4 verpakkingsafmetingen

|

Type |

Parameter |

|

Pakkettype |

672-FBGA (Fineline BGA) |

|

Lichaamsgrootte (L × W) |

27,00 mm × 27,00 mm |

|

Totale pakkethoogte (a) |

Max 3,50 mm |

|

Afstandshoogte (A1) |

Min 0,30 mm |

|

Substraatdikte (A2) |

Max 3,00 mm |

|

Kogeldiameter (b) |

0,50 mm - 0,70 mm |

|

Balveld (e) |

1,00 mm |

|

Aantal ballen |

672 |

|

Montagestijl |

Oppervlaktemontage |

|

Pakketbeschrijving |

FBGA, 27 × 27 mm raster |

EP2S60F672C4 fabrikant

De EP2S60F672C4 FPGA wordt vervaardigd door Altera Corporation, een toonaangevende pionier in programmeerbare logische apparaten.In 2015 werd Altera overgenomen door Intel, en het product valt nu onder Intel's Programmable Solutions Group (PSG), die de gevestigde FPGA -families van Altera blijft ondersteunen en leveren.Intel onderhoudt de Stratix II-lijn als onderdeel van zijn oude productportfolio, voor documentatie, hulpmiddelenondersteuning en beschikbaarheid op lange termijn voor industriële en communicatietoepassingen.

Conclusie

De EP2S60F672C4 combineert een hoge logische dichtheid, flexibele geheugenarchitectuur en robuuste I/O -functies ter ondersteuning van complexe digitale systemen.Het ALM-gebaseerde ontwerp, TRIMATRIX ™ -geheugen, DSP-blokken en klokbeheerfuncties maken een efficiënte implementatie van veeleisende toepassingen mogelijk.Hoewel het bewezen betrouwbaarheid en volwassen ontwikkelingsondersteuning biedt, wordt het geconfronteerd met beperkingen zoals veroudering en gebrek aan moderne transceivers in vergelijking met nieuwere FPGA -generaties.Over het algemeen maken de evenwichtige prestaties en veelzijdigheid het een solide keuze voor signaalverwerking, communicatie, gegevensverwerking en prototyping -toepassingen.

Datasheet PDF

EP2S60F672C4 datasheets:

Over ons

ALLELCO LIMITED

Lees verder

Quick Inviry

Stuur een aanvraag, we zullen onmiddellijk reageren.

Veel Gestelde Vragen [FAQ]

1. Kan EP2S60F672C4 werken met moderne DDR -geheugeninterfaces?

Ja, het ondersteunt DDR-, DDR2-, QDR -II- en RLDRAM II -interfaces, die veel gebruikelijke externe geheugenstandaarden behandelen.Dit maakt het geschikt voor toepassingen met high-bandbreedte gegevensverwerking.

2. Heeft EP2S60F672C4 speciale afhandeling of opslag nodig?

Ja, net als andere BGA-verpakte componenten, moet het worden opgeslagen in vochtgecontroleerde verpakkingen en worden behandeld met ESD-bescherming.Het volgen van de juiste opslagpraktijken helpt bij het handhaven van soldeerbaarheid en de betrouwbaarheid van het apparaat tijdens de montage.

3. Hoe kunt u het stroomverbruik in EP2S60F672C4 -ontwerpen verminderen?

U kunt het logische gebruik, GATE-ongebruikte klokken, lagere I/O-spanningen waar mogelijk optimaliseren en gebruikmaken van stroombewuste synthese-opties in Quartus II om de totale stroomtekening te minimaliseren.

4. Welke programmeerhulpmiddelen zijn vereist voor EP2S60F672C4?

U hebt Intel Quartus II-software nodig voor ontwerp, compilatie en programmering, samen met een USB-blaster of compatibele JTAG-kabel om het apparaat te configureren.

5. Ondersteunt de EP2S60F672C4 in-veldupdates of herconfiguratie op afstand?

Ja, het ondersteunt op AES gebaseerde bitstream-codering en herconfiguratie op afstand, zodat u uw systeem veilig kunt bijwerken zonder de FPGA fysiek te vervangen.

Alles over LFXP6C-3FN256C rooster halfgeleider

Op 2025/10/6

XC2C256-7TQ144C CPLD: PINOUT, FUNCTIES, PROGRAMMING EN GEBRUIKT

Op 2025/10/3

Populaire berichten

-

Complexe instructieset computers: hoe ze de computer hebben gewijzigd?

Op 8000/04/18 147778

-

USB-C-pinout en functies

Op 2000/04/18 112032

-

Met behulp van Xilinx Unified Simulation Primitives: een uitgebreide gids voor FPGA -ontwerp en simulatie

Op 1600/04/18 111351

-

Voedingsspanningen in elektronica: betekenis van VCC, VDD, VEE, VSS en GND

Op 0400/04/18 83788

-

RJ45 -connectorhandleiding: pinout, bedrading, kabeltypen en gebruik

Op 1970/01/1 79589

-

De ultieme gids voor draadkleurcodes in moderne elektrische systemen

De manier waarop onze elektrische systemen kleuren gebruiken, is niet alleen voor uiterlijk.Elke draadkleur geeft nu een specifieke functie aan, waardoor het gemakkelijker wordt om elektrische comp...Op 1970/01/1 66973

-

PURGE VLEP GIDS: Functie, symptomen, testen en vervanging voor optimale motorprestaties

De Purge -klep is een belangrijk onderdeel van het systeem van een auto dat helpt de lucht schoon te houden door brandstofdampen te beheren voordat ze in de atmosfeer kunnen ontsnappen.Dit helpt ni...Op 1970/01/1 63109

-

Kwaliteit (Q) Factor: vergelijkingen en toepassingen

De kwaliteitsfactor, of 'Q', is belangrijk bij het controleren hoe goed inductoren en resonatoren werken in elektronische systemen die radiofrequenties gebruiken (RF).'Q' meet hoe goed een circuit ...Op 1970/01/1 63043

-

Piekprestaties bereiken met de maximale stelling van de stroomoverdracht

De maximale stelling van de stroomoverdracht legt uit hoe energie van een bron, zoals een batterij of generator, naar een aangesloten belasting stroomt.Het toont de exacte voorwaarde waar de belast...Op 1970/01/1 54097

-

A23 Batterijspecificaties en compatibiliteit

De A23-batterij is een kleine, cilindervormige batterij met hoge spanning.Ook wel 23A, 23ae of MN21 genoemd, het loopt op 12 volt en veel hoger dan AA- of AAA -batterijen.Het speciale ontw...Op 1970/01/1 52195