LC5768MC-75F256C CPLD: functies, specificaties, voordelen en toepassingen

Deze gids legt de LC5768MC-75F256C uit, een kleine maar krachtige chip gemaakt door Semiconductor van het rooster.Het laat zien wat de chip doet, hoe het werkt, hoe het te programmeren en waar het kan worden gebruikt.Als u op zoek bent naar een chip die logische taken afhandelt, laag vermogen gebruikt en op veel apparaten werkt, zal deze gids u helpen begrijpen waarom de LC5768MC-75F256C een goede optie is.Catalogus

Wat is de LC5768MC-75F256C?

De LC5768MC-75F256C is een hoogwaardige complex programmeerbaar Logic Device (CPLD), onderdeel van de ISPXPLD 5000MC-familie.Dit apparaat is ontworpen rond een 1,8V kernarchitectuur en biedt een robuuste logische dichtheid, waarbij 768 macrocellen worden geïntegreerd.Als lid van de 5000MC-serie vertegenwoordigt het de geavanceerde CPLD-oplossingen van Lattice die betrouwbare timingcontrole, efficiënte logische implementatie en lage vermogensbewerking bieden, allemaal geoptimaliseerd voor ingebedde en snelle digitale systemen.De ISPXPLD 5000MC-familie verbetert de mogelijkheden van traditionele CPLD's door multifunctionele blokken (MFB's) en flexibele I/O-ondersteuning te introduceren, waardoor de LC5768MC-75F256C een solide keuze is voor schaalbare logische integratie.Met zijn bewezen betrouwbaarheid en architectuur op maat gemaakt voor deterministische prestaties, dient dit apparaat als een betrouwbare bouwsteen in digitaal ontwerp.

Op zoek naar LC5768MC-75F256C?Neem contact met ons op om de huidige voorraad, doorlooptijd en prijzen te controleren.

LC5768MC-75F256C Functies

• 768 Macrocells (op MFB gebaseerde architectuur)

Het apparaat integreert 768 macrocellen georganiseerd in geavanceerde multifunctionele blokken (MFB's), ter ondersteuning van logica met hoge dichtheid met ingebedde reken- en geheugenmogelijkheden.Deze MFB's maken flexibele configuratie mogelijk voor logica-, dual-port SRAM-, FIFO- en CAM-functies.

• 1.8V kernspanning (MC Variant)

Deze MC-serie-variant werkt met een 1,8V-kern en biedt een lager stroomverbruik voor draagbare en zeer efficiënte ontwerpen.Ondanks de lage spanning handhaaft het robuuste prestaties en logische dichtheid.

• 7.5 NS Voortplantingsvertraging (snelheidsgrade -75)

Het bereikt een maximale pin-to-pins propagatievertraging van slechts 7,5 nanoseconden, waardoor het geschikt is voor matige tot high-speed digitale toepassingen.De balances van -75 snelheid in evenwicht en snelheid in ingebedde systemen.

• 193 programmeerbare I/O -pinnen

De chip biedt 193 I/O -pinnen die meerdere spanningsstandaarden en protocollen ondersteunen.Deze pennen zijn volledig programmeerbaar en maken flexibele interface mogelijk met andere logica of analoge apparaten.

• Superwide logische ondersteuning (tot 136 ingangen per blok)

Elke MFB ondersteunt zeer brede logische functies met maximaal 136 invoersignalen, waardoor complexe combinatie -logica in minder logische niveaus mogelijk wordt.Dit vermindert de vertraging van de propagatie en vereenvoudigt de logische synthese.

• Embedded Dual-Port SRAM, FIFO en Ternary Cam Support

MFB's zijn configureerbaar om te fungeren als SRAM (enkele/dubbele poort), FIFO's of ternaire inhoud adresseerbaar geheugen.Deze flexibiliteit maakt geheugenrijk logisch ontwerp mogelijk in een compacte CPLD.

• On-Chip PLL (Sysclock ™)

De ingebouwde PLL ondersteunt klokvermenigvuldiging/divisie van 1 x tot 32 ×, faseverschuiving en externe feedback.Het helpt de timing te beheren en scheef te spannen over snelle synchrone systemen.

• Brede I/O Standard Support (SYSIO ™)

De I/O -blokken ondersteunen een breed scala aan signaleringsnormen, waaronder LVCMOS, LVTTL, SSTL, HSTL, GTL+, LVDS en LVPECL.Dit maakt gemengde spanning en differentiaalsignalering op een enkel apparaat mogelijk.

• System-programmeerbaarheid (ISPXP ™)

Het apparaat ondersteunt in-system programmering via IEEE 1532 of SYSCONFIG-interface.Het kan op het bord worden herprogrammeerd zonder het te verwijderen, waardoor ontwerpupdates en herconfiguratie van het veld mogelijk worden.

• Boundary Scant Test (IEEE 1149.1 -conform)

Volledige JTAG-grensscanondersteuning maakt robuuste testen op bordniveau mogelijk mogelijk.Dit zorgt voor naleving van moderne testvereisten en vereenvoudigt validatie in de productie.

• 5V Tolerant I/O

Ondanks een 1,8V -kern zijn de I/O -banken tolerant voor 5V -signalen, ter ondersteuning van legacy -spanningsinterfaces.Dit verbetert de compatibiliteit met oudere systemen en omgevingen met gemengde spanning.

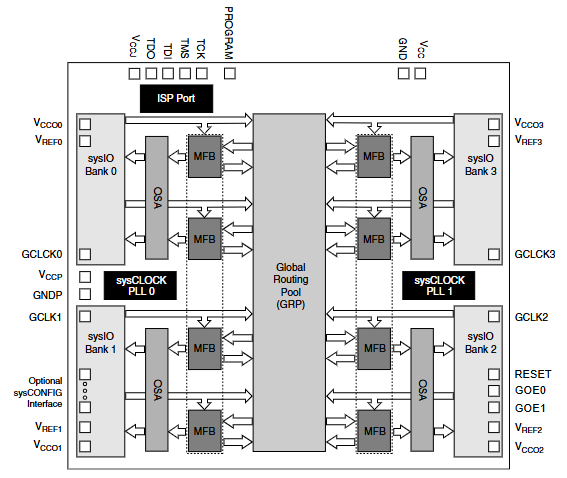

iSPXPLD 5000mx/5000mc blokdiagram

Het blokdiagram van de LC5768MC-75F256C in de ISPXPLD 5000mx/5000mc-familie benadrukt hoe de chip is gestructureerd om programmeerbare logische taken aan te kunnen.In het midden bevindt zich de Global Routing Pool (GRP), die fungeert als de hoofdverbindingshub, die verschillende logica en functionele blokken koppelt, zodat signalen efficiënt kunnen bewegen over het apparaat.Aan weerszijden van de GRP bevinden zich twee fase-vergrendelde lussen (PLL0 en PLL1), onderdeel van het sysclock-systeem.Deze genereren precieze en verstelbare kloksignalen die helpen bij het handhaven van de timingnauwkeurigheid voor snelle bewerkingen over de chip.

Rond de GRP en PLL's zijn vier Sysio -banken.Elke bank bevat configureerbare systeemarrays (CSA's) en multifunctionele blokken (MFB's).De CSA's behandelen basistische logica -verwerking, terwijl de MFBS meer geavanceerde functies ondersteunen, zoals wiskundige bewerkingen en geheugenfuncties.Deze opstelling geeft het apparaat een sterke I/O -flexibiliteit en maakt het gemakkelijker om op te schalen voor verschillende toepassingen.Power- en klokverbindingen worden ook duidelijk weergegeven in het diagram.Meerdere VCC-, VREF- en GND -pennen worden verdeeld om stabiele kracht over de chip te behouden.Globale klokinvoer (GCLK0 naar GCLK3) laten externe klokken in het systeem en werken met de GRP en PLLS.

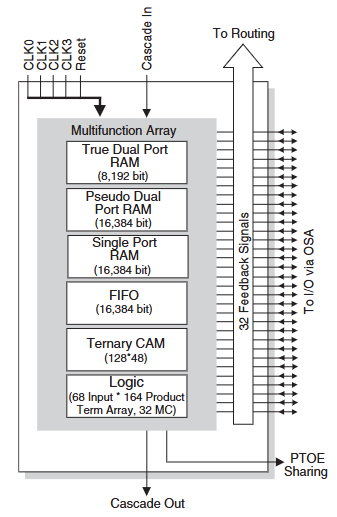

Multifunctionele blok (MFB) diagram

Het multifunctionele blok (MFB) in de LC5768MC-75F256C ISPXPLD 5000mx/5000mc combineert zowel geheugen- als logische functies ter ondersteuning van flexibele ontwerpbehoeften.Het ondersteunt verschillende geheugentypen, waaronder echte dubbele poort RAM (8.192 bits), pseudo dual port ram, FIFO en enkele poort RAM (elk tot 16.384 bits), plus ternaire cam (128 × 48).Deze geheugenopties maken de MFB nuttig voor gegevensbuffering, tijdelijke opslag en snelle gegevensopzoek.

De MFB heeft ook sterke logische mogelijkheden.Het omvat een 68-input door 164-product term array en 32 macrocellen, waardoor het complexe logische bewerkingen kan uitvoeren.Het maakt gebruik van meerdere klokinvoer (CLK0 naar CLK3) en een resetsignaal om timing en bewerkingen te regelen.Om de functionaliteit uit te breiden, kunnen cascade -in/uit -poorten MFB's met elkaar worden aangesloten over blokken.De QSA -interface (Quad System Array) verbindt de MFB met I/O -banken voor snelle communicatie met externe systemen.Kortom, de MFB is een krachtige, flexibele eenheid die zowel geheugen- als logische taken verwerkt, waardoor het apparaat goed presteert in ingebedde en hogesnelheidstoepassingen.

LC5768MC-75F256C specificaties

|

Type |

Parameter |

|

Fabrikant |

Lattice Semiconductor Corporation |

|

Serie |

ISPXPLD® 5000 |

|

Verpakking |

Bulk |

|

Onderdeelstatus |

Actief |

|

Programmeerbaar type |

In systeem programmeerbaar |

|

Vertragingstijd TPD (1) Max |

7.5 ns |

|

Spanningsvoorziening - Intern |

1.65V ~ 1.95V |

|

Aantal logische elementen/blokken |

24 |

|

Aantal macrocellen |

768 |

|

Aantal I/O |

193 |

|

Bedrijfstemperatuur |

0 ° C ~ 90 ° C (TJ) |

|

Montagetype |

Oppervlaktemontage |

|

Pakket / kast |

256-BGA |

|

Leverancierapparaatpakket |

256-FPBGA (17x17) |

LC5768MC-75F256C-toepassingen

1. Telecommunicatie en netwerken

De LC5768MC-75F256C is ideaal voor gebruik in basisstations, telecomschakelaars en optische netwerkeenheden, waar hoge snelheid en deterministische logica nodig zijn.Het ingebedde geheugen en multi-spanning I/O-ondersteuningsteun schakelen protocolverwerking, gegevensframing en lage-latentiebesturingstaken mogelijk.

2. Gegevenscommunicatie en opslag

Deze CPLD is goed geschikt voor routers, RAID-controllers en schijf-array-systemen die efficiënte gegevensverwerking en snelle signaalverwerking vereisen.De SRAM- en FIFO-ondersteuning met dubbele poorts bieden de buffering en stroomregeling die nodig is in omgevingen met hoge doorvoer.

3. Protocol -processors en businterfaces

Met voorspelbare timing en logische bronnen met hoge dichtheid blinkt de LC5768MC uit in de implementatie van busbruggen, backplane-interfaces en protocoldecoders.Het maakt snelle logische antwoorden mogelijk en ondersteunt naadloze integratie met meerdere signaleringsnormen.

4. Industriële en IoT -besturingssystemen

In industriële automatisering wordt het apparaat gebruikt voor monitoring-, machinebestrijdings- en logische sequencing.De instant-on capaciteit, low power tekening en robuuste I/O-functies maken het geschikt voor IoT-knooppunten en ingebedde controllers.

5. Consumenten- en medische elektronica

De compacte voetafdruk en rijke logica-gemengde memory-mogelijkheden maken deze CPLD waardevol in draagbare medische instrumenten en consumentenelektronica.Het behandelt systeembesturing, interfacebeheer en vermogenssequencing in grootte-beperkte en energiegevoelige ontwerpen.

LC5768MC-75F256C vergelijkbare onderdelen

|

Functie |

LC5768MC-75F256C |

LC5768MV-75F484C |

LC5768MV-75FN256C |

LC5768MV-5F484C |

|

Familie |

ISPXPLD 5000MC |

ISPXPLD 5000MV |

ISPXPLD 5000MV |

ISPXPLD 5000MV |

|

Kernspanning |

1.8V |

3.3V |

3.3V |

3.3V |

|

Macrocellen |

768 |

768 |

768 |

768 |

|

Maximale frequentie |

~ 150 MHz |

~ 150 MHz |

~ 150 MHz |

~ 200–250MHz |

|

Voortplantingsvertraging (TPD) |

7.5ns |

7.5ns |

7.5ns |

5ns |

|

Pakkettype |

256-ball BGA |

484-ball BGA |

256-ball BGA |

484-ball BGA |

|

Pakketcode |

F256C |

F484C |

FN256C |

F484C |

|

I/o tellen |

193 |

317 |

193 |

317 |

|

In-system programmeerbaar |

Ja |

Ja |

Ja |

Ja |

|

Ingebed geheugenondersteuning |

Ja (SRAM/FIFO/CAM) |

Ja |

Ja |

Ja |

|

JTAG (IEEE 1149.1) |

Ondersteund |

Ondersteund |

Ondersteund |

Ondersteund |

|

Instant-on |

Ja |

Ja |

Ja |

Ja |

|

Sollicitatie |

Laagkracht, dichte logica |

High I/O, algemene CPLD |

Compact 3.3V logica |

High-speed 3.3V logica |

LC5768MC-75F256C programmeerstappen

1. Bereid uw bord en tools voor

Sluit de LC5768MC-75F256C aan op uw pc met behulp van een compatibele programmeerkabel zoals het rooster HW-USBN-2B.Zorg ervoor dat JTAG -lijnen correct worden gerouteerd en beëindigingsweerstanden (bijv. 4,7kΩ op TCK) zijn aanwezig om stabiele communicatie te garanderen.

2. Genereer het programmeerbestand

Gebruik Lattice Diamond of ISPVM -software om uw ontwerp samen te stellen en een programmeerbestand Jedec (.Jed) te exporteren.Dit bestand bevat de volledige bitstream die in het configuratiegeheugen van de CPLD wordt geschreven.

3. Start de programmeersoftware

Open de diamantprogrammeur- of ISPVM -systeemtool op uw pc en controleer of uw programmeur correct is gedetecteerd.Selecteer het LC5768MC-75F256C-apparaat uit de lijst om te starten.

4. Voer in-system programmering uit (ISP)

Gebruik de JTAG (IEEE 1532) -interface om het JEDEC -bestand rechtstreeks in het apparaat te laden terwijl het op het bord blijft gemonteerd.De bitstream wordt opgeslagen in intern niet-vluchtig geheugen, waardoor instant-on configuratie bij opstarten mogelijk wordt.

5. Controleer en beveilig de configuratie

Voer na het programmeren een read-back-bewerking uit om te bevestigen dat de configuratie succesvol was.Activeer indien nodig de beveiligingszekering om het apparaat te vergrendelen en ongeautoriseerde herprogrammering of reverse engineering te voorkomen.

6. Configureer en reset het apparaat

Zodra het programmeren is voltooid, kan het apparaat automatisch opnieuw worden gestart of kunt u zijn programma of init -pinnen schakelen om een herlaad te forceren.De CPLD werkt vervolgens op basis van de nieuw toegepaste configuratie met deterministische opstarttiming.

7. Optioneel: herprogrammering of updates van het veld

U kunt de LC5768MC-75F256C in het veld herprogrammeren met dezelfde JTAG-interface voor updates of correcties.Bovendien maakt de SYSCONFIG ™ -interface gedeeltelijke herconfiguratie mogelijk zonder volledige stroomfietsen in geavanceerde toepassingen.

LC5768MC-75F256C Voordelen

• Lagere stroombewerking voor draagbare en ingebedde systemen

Vergeleken met veel traditionele CPLD's met hogere kernspanningen, helpt de LC5768MC-75F256C's laagkracht 1,8V-kern de het totale systeemverbruik van het systeem te verminderen.Dit maakt het aantrekkelijk voor op batterijen bediende of warmtegevoelige toepassingen waar het thermische budget en energie-efficiëntie van belang zijn.

• Direct vermogen

In tegenstelling tot veel FPGA's of grotere programmeerbare apparaten die bij elke startup externe configuratie vereisen, biedt deze CPLD direct gedrag, waardoor vertragingen of de behoefte aan extern flash-geheugen kunnen voorkomen.Dit leidt tot snellere time-to-operation en grotere betrouwbaarheid.

• Meer voorspelbare timing versus fpgas

Het deterministische timinggedrag van deze CPLD, vooral onder zware logica of I/O-belastingen, geeft een betere controle in vergelijking met de vaak variabele timing van grotere FPGA's.Dit maakt het geschikter voor tijdkritische toepassingen zoals digitale bedieningslussen, communicatie-interfaces en gesynchroniseerde logische systemen.

• Efficiënte leercurve en ontwerptool ecosysteem

Voor de overgang van 22V10s, oudere PAL/GALS of eenvoudige PLD's, biedt dit apparaat een zachte leercurve via de intuïtieve ontwerptools van Lattice zoals Diamond en ISPVM.Velen profiteren van snellere prototyping en minder integratiehoofdpijn.

LC5768MC-75F256C verpakkingsafmetingen

• Pakkettype: Fine-Pitch Ball Grid Array

• Telling: 256 ballen

• Pakketmaat: 17 mm × 17 mm

• Pakkethoogte: Ongeveer 1,2 mm

• Ball -pitch: Standaard fine-pitch meestal 0,8 mm

LC5768MC-75F256C fabrikant

De LC5768MC-75F256C wordt vervaardigd door Lattice Semiconductor Corporation, een in de VS gevestigd bedrijf erkend voor zijn expertise in low-power, programmeerbare logische apparaten met kleine voeten.Opgericht in 1983 en met hoofdkantoor in Hillsboro, Oregon, richt Lattice zich op het leveren van FPGA's, CPLD's en gerelateerde ontwikkelingstools die zijn op maat gemaakt voor applicaties in communicatie, computing, industriële, automobiel- en consumentenmarkten.Het bedrijf staat bekend om lange productlevenscycli, brede ontwerptoolondersteuning en betrouwbare programmeerbaarheid in het systeem in zijn apparaatfamilies.Als de oorspronkelijke ontwikkelaar en leverancier van de ISPXPLD® 5000mc-familie, zorgt Relatice voor robuuste technische documentatie, softwareondersteuning en beschikbaarheid door geautoriseerde distributeurs en langdurige levenscycluspartners.

Conclusie

De LC5768MC-75F256C is een slimme en betrouwbare CPLD die sterke logica- en geheugenfuncties biedt in één compacte chip.Het gebruikt weinig vermogen, start direct op en werkt met veel verschillende signaaltypen.Met 768 macrocellen, ingebouwd geheugen, snelle klokken en flexibele invoer-/uitvoeropties, past het goed in producten zoals telecomapparaten, industriële machines, opslagsystemen en consumentenelektronica.De eenvoudige programmering, sterke prestaties en ondersteuning voor updates maken het een nuttige oplossing voor zowel nieuwe ontwerpen als upgrades.

Over ons

ALLELCO LIMITED

Lees verder

Quick Inviry

Stuur een aanvraag, we zullen onmiddellijk reageren.

Veel Gestelde Vragen [FAQ]

1. Kan ik de LC5768MC-75F256C gebruiken in batterijgevoelige of energiegevoelige apparaten?

Ja, het 1.8V kernspanning en het lage ontwerpontwerp van het LC5768MC-75F256C maken het zeer geschikt voor draagbare, batterijbewerkte en thermisch beperkte omgevingen, zoals IoT-knooppunten of medische hulpmiddelen.

2. Is de LC5768MC-75F256C compatibel met Legacy 5V-systemen?

Ja.Zelfs met zijn lage kernspanning heeft de LC5768MC-75F256C 5V-tolerante I/O-banken, waardoor compatibiliteit met legacy-interfaces en gemengde spanningssystemen zorgt zonder dat er extra niveau-verschuivende componenten nodig zijn.

3. Wat voor soort ontwikkelingstools worden ondersteund voor LC5768MC-75F256C-programmering?

De LC5768MC-75F256C wordt ondersteund door rooster Diamond, ISPVM-systeem en de Diamond-programmeur.Deze tools bieden volledige ondersteuning voor ontwerp, simulatie, programmering en foutopsporing die geschikt is voor zowel instap- als geavanceerde gebruikers.

4. Vereist de LC5768MC-75F256C extern geheugen om te werken?

Er is geen extern geheugen vereist voor de configuratie.De LC5768MC-75F256C heeft een niet-vluchtig geheugen en ondersteunt instant-on capaciteiten, waardoor deze onmiddellijk na de power-up kan beginnen zonder externe flits of EEPROM nodig te hebben.

5. Is de LC5768MC-75F256C geschikt voor harde industriële omgevingen?

Ja, met robuuste logische prestaties, brede spanningstolerantie en betrouwbaar opstartgedrag presteert de LC5768MC-75F256C goed in industriële besturingssystemen en fabrieksautomatisering waar stabiele werking nodig is.

EPF8820Arc208-4 FPGA-gids: functies, architectuur, toepassingen en programmeren

Op 2025/07/11

EPF6016ATC144-2N FPGA: Functies, programmering, toepassingen en alternatieven

Op 2025/07/10

Populaire berichten

-

Complexe instructieset computers: hoe ze de computer hebben gewijzigd?

Op 8000/04/18 147767

-

USB-C-pinout en functies

Op 2000/04/18 111994

-

Met behulp van Xilinx Unified Simulation Primitives: een uitgebreide gids voor FPGA -ontwerp en simulatie

Op 1600/04/18 111351

-

Voedingsspanningen in elektronica: betekenis van VCC, VDD, VEE, VSS en GND

Op 0400/04/18 83758

-

RJ45 -connectorhandleiding: pinout, bedrading, kabeltypen en gebruik

Op 1970/01/1 79555

-

De ultieme gids voor draadkleurcodes in moderne elektrische systemen

De manier waarop onze elektrische systemen kleuren gebruiken, is niet alleen voor uiterlijk.Elke draadkleur geeft nu een specifieke functie aan, waardoor het gemakkelijker wordt om elektrische comp...Op 1970/01/1 66952

-

PURGE VLEP GIDS: Functie, symptomen, testen en vervanging voor optimale motorprestaties

De Purge -klep is een belangrijk onderdeel van het systeem van een auto dat helpt de lucht schoon te houden door brandstofdampen te beheren voordat ze in de atmosfeer kunnen ontsnappen.Dit helpt ni...Op 1970/01/1 63098

-

Kwaliteit (Q) Factor: vergelijkingen en toepassingen

De kwaliteitsfactor, of 'Q', is belangrijk bij het controleren hoe goed inductoren en resonatoren werken in elektronische systemen die radiofrequenties gebruiken (RF).'Q' meet hoe goed een circuit ...Op 1970/01/1 63028

-

Piekprestaties bereiken met de maximale stelling van de stroomoverdracht

De maximale stelling van de stroomoverdracht legt uit hoe energie van een bron, zoals een batterij of generator, naar een aangesloten belasting stroomt.Het toont de exacte voorwaarde waar de belast...Op 1970/01/1 54094

-

A23 Batterijspecificaties en compatibiliteit

De A23-batterij is een kleine, cilindervormige batterij met hoge spanning.Ook wel 23A, 23ae of MN21 genoemd, het loopt op 12 volt en veel hoger dan AA- of AAA -batterijen.Het speciale ontw...Op 1970/01/1 52176