FPGA -ontwerp verbeteren met gebruikersbeperkingsbestanden (UCF) voor Xilinx ISE -tools

Deze gids onderzoekt de rol van gebruikersbeperkingsbestanden (UCF's) bij het verbeteren van het FPGA -ontwerp met Xilinx ISE -tools.UCF's laten specifieke beperkingen toe om timing, logica en plaatsing beter te regelen, wat de ontwerpnauwkeurigheid, prestaties en betrouwbaarheid verhoogt.Door te laten zien hoe deze beperkingen effectief toe te passen, helpt de gids het ontwerpproces te vereenvoudigen, de foutopsporingstijd te verminderen en een succesvolle projectlevering te garanderen.Catalogus

Doel en rol van UCF's in FPGA -ontwerp

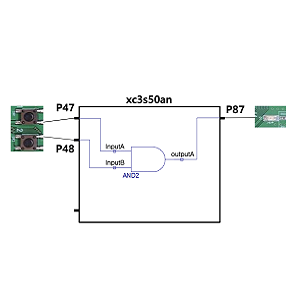

In FPGA -ontwerp spelen gebruikersbeperkingsbestanden (UCF's) een rol bij het controleren van hoe de logica die van uw code wordt gesynthetiseerd, fysiek op de chip wordt geïmplementeerd.Deze bestanden laten belangrijke parameters op, zoals timingbeperkingen, pin -toewijzingen en details van de plaatsingsplaatsing die direct kunnen beïnvloeden of een ontwerp voldoet aan de prestatievereisten of niet.Beschouw UCFS als blauwdrukken die ervoor zorgen dat alles correct wordt geplaatst, werkt op schema en past netjes op zijn plaats.Het proces van beperking begint in de vroege stadia van ontwikkeling.Begin met het maken van een UCF -bestand vóór synthese, zodat parameters vanaf het begin worden vergrendeld.Na synthese worden aanvullende beperkingsbestanden zoals het NetList Constraint -bestand (NCF) en fysieke beperkingsbestand (PCF) gegenereerd om wijzigingen in de logica weer te geven en om fysieke beperkingen te voltooien.Elk van deze bestanden bouwt voort op de vorige stap, waardoor het ontwerp geleidelijk wordt verfijnd.UCF's zijn tekstgebaseerde bestanden geschreven in ASCII-indeling, wat betekent dat ze kunnen worden bewerkt met behulp van basisteksteditors of meer gespecialiseerde tools zoals de Xilinx Constraint Editor.Deze eenvoud maakt UCF's zeer toegankelijk en flexibel om te duiken in de details van beperkingsinstellingen zonder overdreven complexe tools nodig te hebben.

Hoe beperkingen vormen FPGA -ontwerp?

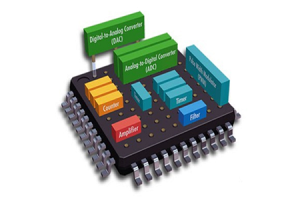

In FPGA -ontwerp spelen beperkingen een rol bij het vormgeven van hoe de chip presteert en interageert met externe apparaten.Deze beperkingen worden gedefinieerd in een UCF (gebruikersbeperkingsbestand), die fungeert als een gedetailleerde instructieset voor de ontwerptool, waarmee wordt aangegeven hoe de interne componenten van de FPGA moeten worden aangesloten en beheerd.Belangrijkste beperkingen omvatten timingbeperkingen, die ervoor zorgen dat signalen tussen componenten binnen een specifiek tijdsbestek reizen om betrouwbare prestaties te behouden met de gewenste kloksnelheid.PIN -toewijzingen brengen fysieke FPGA -pinnen toe aan externe apparaten zoals sensoren, geheugenmodules of communicatie -interfaces, waardoor nauwkeurige verbindingen worden gewaarborgd.Gebiedsbeperkingen regelen de plaatsing van logische blokken op de chip om congestie te voorkomen, vertragingen te verminderen en het gebruik van hulpbronnen te optimaliseren.Zonder deze beperkingen zouden geautomatiseerde tools plaatsing- en routeringsbeslissingen nemen, maar vaak met suboptimale resultaten, wat leidt tot timingproblemen, knelpunten of inefficiënte chiplay -outs.Door UCF -bestanden te gebruiken, behouden velen controle over deze kritieke aspecten, wat resulteert in betere prestaties, efficiëntie en betrouwbaarheid in FPGA -ontwerpen.

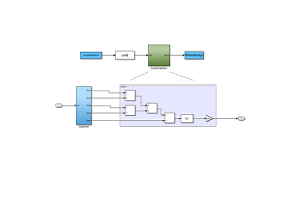

De iteratieve aard van de verfijning van de beperking

FPGA-ontwerp is zelden een eenmalige proces.Beperkingen worden herhaaldelijk aangepast tijdens de ontwikkelingscyclus naarmate het ontwerp evolueert en nieuwe uitdagingen ontstaan.Anderen tweaken UCF -bestanden om prestatiedoelen te bereiken, timingproblemen op te lossen of zich aan te passen aan het wijzigen van projectvereisten.Deze iteratieve verfijning is een belangrijk onderdeel van de FPGA -workflow.Als u bijvoorbeeld merkt dat een signaalpad te lang duurt om zich te verspreiden tussen twee componenten, kunnen ze de UCF aanpassen om de timingbeperking te wijzigen of die componenten te verplaatsen om vertragingen te verminderen.Evenzo, als een pin -toewijzing in strijd is met externe hardware, kan de UCF worden bewerkt om de mismatch op te lossen.Elke herziening van de UCF brengt het ontwerp dichter bij het gewenste resultaat, waarbij elke aanpassing meer onderwijst over de afwegingen die betrokken zijn bij FPGA-optimalisatie.Deze cyclus van testen, aanpassen en leren verbetert niet alleen het ontwerp, maar scherpt ook vaardigheden.

Voordelen van het gebruik van UCF's

Het toepassen van beperkingen via UCF -bestanden biedt verschillende praktische voordelen die bijdragen aan het succes van FPGA -projecten:

• Verbeterde timingnauwkeurigheid: goed gemaakte timingbeperkingen zorgen ervoor dat de FPGA betrouwbaar werkt met de gewenste kloksnelheid, waardoor fouten worden veroorzaakt veroorzaakt door signaalvertragingen.

• Betere gebruik van middelen: gebiedsbeperkingen voorkomen dat logische blokken te dicht bij elkaar of te ver uit elkaar worden geplaatst, het optimaliseren van chipruimte en het verbeteren van de prestaties.

• Vereenvoudigde foutopsporing: door het besturen van pin -toewijzingen en signaalroutering helpen UCF's routeringsconflicten te verminderen, waardoor het gemakkelijker wordt om problemen tijdens het testen te diagnosticeren en op te lossen.

Over ons

ALLELCO LIMITED

Lees verder

Quick Inviry

Stuur een aanvraag, we zullen onmiddellijk reageren.

Toepassingsspecifieke standaardproducten (ASSPS): innovatie in moderne elektronica stimuleren

Op 2025/01/8

Systeem op een programmeerbare chip (SOPC): technologie, ontwerp en toepassingen

Op 2025/01/8

Populaire berichten

-

Complexe instructieset computers: hoe ze de computer hebben gewijzigd?

Op 8000/04/19 147780

-

USB-C-pinout en functies

Op 2000/04/19 112050

-

Met behulp van Xilinx Unified Simulation Primitives: een uitgebreide gids voor FPGA -ontwerp en simulatie

Op 1600/04/19 111352

-

Voedingsspanningen in elektronica: betekenis van VCC, VDD, VEE, VSS en GND

Op 0400/04/19 83806

-

RJ45 -connectorhandleiding: pinout, bedrading, kabeltypen en gebruik

Op 1970/01/1 79608

-

De ultieme gids voor draadkleurcodes in moderne elektrische systemen

De manier waarop onze elektrische systemen kleuren gebruiken, is niet alleen voor uiterlijk.Elke draadkleur geeft nu een specifieke functie aan, waardoor het gemakkelijker wordt om elektrische comp...Op 1970/01/1 66991

-

PURGE VLEP GIDS: Functie, symptomen, testen en vervanging voor optimale motorprestaties

De Purge -klep is een belangrijk onderdeel van het systeem van een auto dat helpt de lucht schoon te houden door brandstofdampen te beheren voordat ze in de atmosfeer kunnen ontsnappen.Dit helpt ni...Op 1970/01/1 63113

-

Kwaliteit (Q) Factor: vergelijkingen en toepassingen

De kwaliteitsfactor, of 'Q', is belangrijk bij het controleren hoe goed inductoren en resonatoren werken in elektronische systemen die radiofrequenties gebruiken (RF).'Q' meet hoe goed een circuit ...Op 1970/01/1 63050

-

Piekprestaties bereiken met de maximale stelling van de stroomoverdracht

De maximale stelling van de stroomoverdracht legt uit hoe energie van een bron, zoals een batterij of generator, naar een aangesloten belasting stroomt.Het toont de exacte voorwaarde waar de belast...Op 1970/01/1 54097

-

A23 Batterijspecificaties en compatibiliteit

De A23-batterij is een kleine, cilindervormige batterij met hoge spanning.Ook wel 23A, 23ae of MN21 genoemd, het loopt op 12 volt en veel hoger dan AA- of AAA -batterijen.Het speciale ontw...Op 1970/01/1 52199