EPM7160ELC84-15: Datasheet, Functies, Pinout, Programming and Applications

Deze gids gaat over de EPM7160ELC84-15, een speciale chip die helpt bij het bouwen van aangepaste digitale logische circuits.U kunt het programmeren met behulp van een JTAG -verbinding en deze zelfs bijwerken terwijl deze al in uw systeem is geïnstalleerd.Het heeft ook beveiligingsfuncties om uw ontwerp te beschermen.Dit artikel legt alles uit over de chip, inclusief de pin -lay -out, functies, gebruik en hoe het te programmeren.Of u nu werkt aan machines, auto's of netwerkapparatuur, deze handleiding helpt u te begrijpen waarom deze chip nuttig is.Catalogus

EPM7160ELC84-15 Overzicht

De EPM7160ELC84-15 maakt deel uit van Intel's Max 7000-serie CPLD's, die de geavanceerde Max Architecture van Altera gebruiken.Deze apparaten, gefabriceerd met hoogwaardige CMOS-technologie, zijn afgestemd op hoge dichtheid en krachtige digitale logische circuitimplementaties.Dit model beschikt over 160 macrocellen en biedt ongeveer 3.200 bruikbare poorten, die tegemoet komen aan de behoeften van complexe digitale systemen.Het werkt op een 5V-toevoer, met een typische pin-to-pins vertraging van 15 ns, waardoor de countersnelheden tot 175,4 MHz mogelijk zijn, waardoor een snelle signaalverwerking en efficiënte systeemprestaties worden gewaarborgd.Deze CPLD ondersteunt zowel in-system programmering als herprogrammering via een geïntegreerde JTAG-interface, die voldoet aan IEEE STD.1149.1, het verbeteren van de flexibiliteit en het gemak van updates na installatie.Het biedt ook een beveiligingsbitfunctie om ongeautoriseerd kopiëren van configuratiegegevens te voorkomen, een waardevolle toevoeging voor het beschermen van intellectueel eigendom.

Als u alles wilt beveiligen wat uw bedrijf nodig heeft, is dit het perfecte moment om een bulkorder bij ons te plaatsen.We zijn klaar om u te helpen tijd te besparen, kosten te besparen en precies te krijgen wat u nodig hebt.

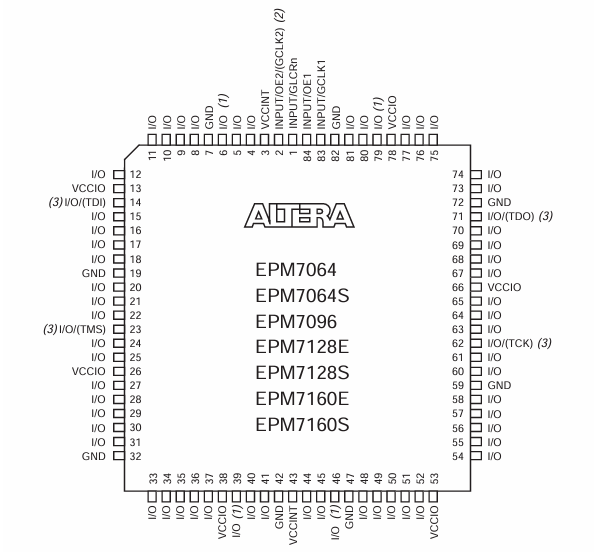

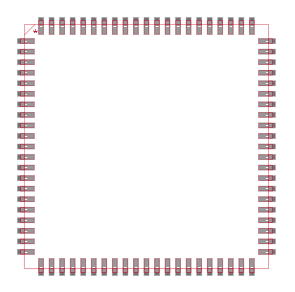

EPM7160ELC84-15 Pinout-diagram

Het pinout -diagram voor de EPM7160ELC84-15 Apparaat illustreert de fysieke lay -out en functionaliteit van zijn 84 pennen in een PLCC -pakket (plastic loodcrager).Het diagram toont een vierkante configuratie, waarbij aan elke pin een specifiek label is toegewezen dat de functie ervan aangeeft, zoals IO (invoer/uitvoer), GND (grond), of VCCIO (Voedingsspanning voor I/O).Pinnen gelabeld als IO Vertegenwoordig configureerbare digitale invoer- of uitvoerlijnen, die worden gebruikt om te communiceren met andere apparaten in een circuit. VCCIO pins leveringsspanning naar de I/O -banken, En GND Pinnen bieden de grondreferentie.Speciale functiepennen omvatten TDI,, TDO,, TMS, En Tck, die worden gebruikt voor Jtag Programmering en grenzenscans testen.Bovendien, pins zoals Input1/clk1 En Input2/clk2 zijn aangewezen klok- of besturingssignaalingangen voor interne logische timing.

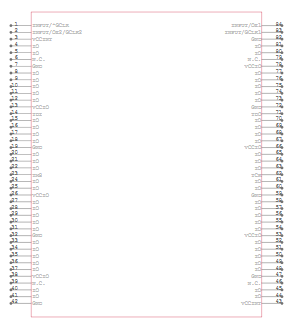

EPM7160ELC84-15 CAD-modellen

EPM7160ELC84-15 symbool

EPM7160ELC84-15 voetafdruk

EPM7160ELC84-15 3D-model

EPM7160ELC84-15 functies

• Hoge dichtheid logica: De EPM7160ELC84-15 biedt 160 macrocellen en ongeveer 3.200 bruikbare poorten, waardoor het zeer geschikt is voor complexe digitale ontwerpen.Deze dichtheid maakt het mogelijk om meerdere functies in een enkel apparaat te integreren, waardoor compactere en efficiënte circuitontwerpen worden vergemakkelijkt.

• Snelle prestaties: Met een maximale voortplantingsvertraging van 15 ns en de mogelijkheid om werkfrequenties tot 100 MHz te ondersteunen, zorgt deze CPLD voor snelle signaalverwerking en snelle prestaties voor tijdgevoelige toepassingen.

• System-programmeerbaarheid (ISP): Met een ingebouwde IEEE STD.1149.1 (JTAG) interface, het apparaat ondersteunt programmering in het systeem.Met deze mogelijkheid kan het apparaat na installatie worden geprogrammeerd en opnieuw geprogrammeerd, waardoor flexibiliteit wordt gebracht voor updates en functionaliteitswijzigingen zonder dat fysieke vervanging nodig is.

• Multivolt ™ I/O -interface : De Multivolt I/O -interface ondersteunt verschillende bedrijfsspanningen, waardoor de CPLD compatibel wordt met 5,0 V, 3,3 V en 2,5 V logische niveaus.Met deze functie kan het apparaat worden gebruikt in gemengde spanningssystemen, waardoor het aanpassingsvermogen aan verschillende elektronische omgevingen wordt verbeterd.

• Flexibele I/O -configuratie: Het biedt 64 programmeerbare I/O -pinnen die veelzijdige interface -opties bieden.Deze flexibiliteit is belangrijk voor toepassingen die een verscheidenheid aan invoer-/uitvoerconfiguraties vereisen, wat een breed scala aan connectiviteit en functionaliteit ondersteunt.

• EEPROM-gebaseerd geheugen: Gebruik van EEPROM -technologie voor configuratieopslag, kan de CPLD tot 100 keer worden herprogrammeerd.Dit niet-vluchtige geheugen zorgt ervoor dat het apparaat zijn configuratie behoudt, zelfs na stroomcycli voor betrouwbaarheid en onderhoudsgemak.

• Beveiligingsfuncties: Het apparaat bevat een beveiligingsbit dat ongeautoriseerde toegang tot de geprogrammeerde logica voorkomt, intellectueel eigendom beschermt en het voorkomen van manipulatie, wat goed is voor applicaties in beveiligingsgevoelige omgevingen.

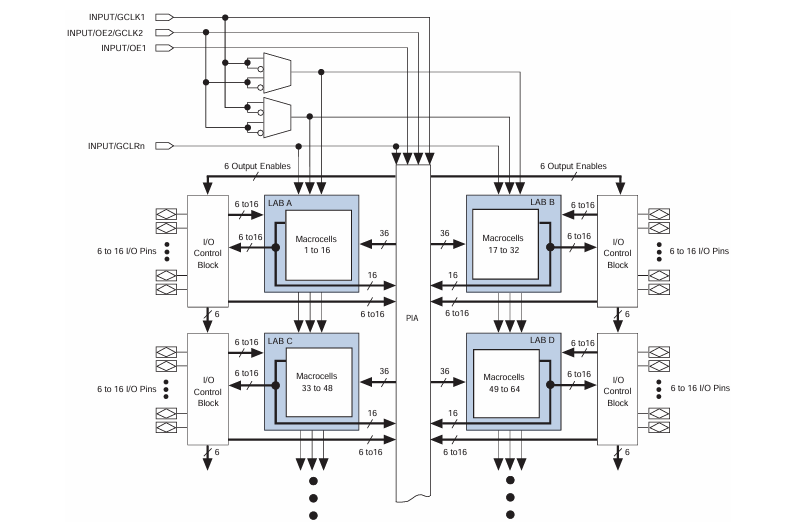

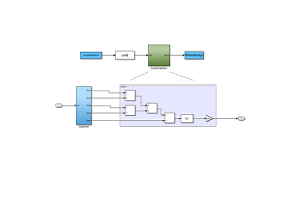

Blokdiagram

Het blokdiagram van de EPM7160ELC84-15, vertegenwoordigt een goed gestructureerde interne architectuur bestaande uit vier Logicarray Blocks (Labs) gelabeld A,, B,, C, En D.Elk lab bevat 16 Macrocells, het maken van een totaal van 64 Macrocells, die de bouwunits zijn voor het maken van logische functies.Deze macrocellen kunnen combinatie- of geregistreerde logica implementeren met behulp van programmeerbare interconnects en bedieningssignalen.In het midden, de Programmable Interconnect Array (PIA) dient als de communicatie -ruggengraat, waardoor flexibele routing van signalen tussen Laboratorium En IO pinnen.Elk laboratorium maakt verbinding met de PIA met 36 ingangslijnen en 16 uitvoerlijnen, waardoor een hoge mate van logische interconnectiviteit wordt gewaarborgd.Rond de periferie, I/O -besturingsblokken Beheer invoer- en uitvoersignalen en biedt tussen de 6 en 16 I/O -pinnen per zijde, die rechtstreeks samenwerken met het externe systeem.Het toont ook globale besturingssignalen zoals klok (GCLK1, GCLK2), output Enable (OE1) en Clear (Gclrn) gedistribueerd naar alle laboratoria voor gesynchroniseerde en gecentraliseerde logische besturing.Deze signalen kunnen worden geleid via multiplexers om ontwerpflexibiliteit en efficiëntie te bieden.

EPM7160ELC84-15 Specificaties

|

Type |

Parameter |

|

Fabrikant |

Altera/intel |

|

Serie |

Max® 7000 |

|

Verpakking |

Buis |

|

Onderdeelstatus |

Verouderd |

|

Programmeerbaar type |

EE PLD |

|

Vertragingstijd TPD (1) Max |

15 ns |

|

Spanningsvoorziening - Intern |

4.75V ~ 5.25V |

|

Aantal logische elementen/blokken |

10 |

|

Aantal macrocellen |

160 |

|

Aantal poorten |

3200 |

|

Aantal I/O |

64 |

|

Bedrijfstemperatuur |

0 ° C ~ 70 ° C (TA) |

|

Montagetype |

Oppervlaktemontage |

|

Pakket / kast |

84-LCC (J-Lead) |

|

Leverancierapparaatpakket |

84-PLCC (29.31x29.31) |

|

Base Productnummer |

EPM7160 |

EPM7160ELC84-15 Toepassingen

Industriële automatisering

In de industriële automatisering wordt de EPM7160ELC84-15 gebruikt om de logica te regelen binnen programmeerbare logische controllers (PLC's), motorcontrollers en sensorinterfaces.Het vermogen om complexe logische bewerkingen en snelle I/O -omschakelen te verwerken, maakt het ideaal voor automatiseringstaken die nauwkeurige controle en timing vereisen.

Ingebedde systemen

Deze CPLD is nuttig in ingebedde systemen waar ruimte en krachtefficiëntie belangrijk zijn.Het vindt applicaties in robotica, Internet of Things (IoT) -apparaten en consumentenelektronica, waar de programmeerbaarheid ervan mogelijk is aanpassing en aanpassingsvermogen aan specifieke functionele vereisten.

Telecommunicatie

Het apparaat wordt gebruikt in telecommunicatieapparatuur zoals routers en schakelaars voor het beheren van timing, gegevensroutering en protocolafhandeling.De snelle prestaties en het vermogen om op verschillende spanningsniveaus te werken, maken het geschikt voor netwerkinfrastructuur die betrouwbaarheid en hoge gegevensdoorvoer vereist.

Auto -elektronica

Binnen de automobielsector ondersteunt de EPM7160ELC84-15 toepassingen in infotainmentsystemen, lichaamscontrolemodules en motorbeheereenheden.De robuustheid en ondersteuning van de CPLD voor een breed scala aan invoer/uitgangsspanningen stelt het in staat om betrouwbaar te presteren in de veeleisende omstandigheden van automobielomgevingen.

Medische hulpmiddelen

De CPLD wordt ook toegepast in technologie voor medische hulpmiddelen, met name in diagnostische apparatuur en patiëntenbewakingssystemen.De beveiligingsfuncties en stabiele werking onder verschillende omgevingscondities zorgen ervoor dat het veilig en efficiënt gevoelige en gezondheidszorgtoepassingen aan kan.

EPM7160ELC84-15 vergelijkbare onderdelen

EPM7160ELC84-15 programmeerstappen

Het programmeren van de EPM7160ELC84-15, een CPLD uit de Max 7000-serie van Intel, omvat een gestructureerd proces om ervoor te zorgen dat het apparaat werkt volgens specificaties.Hier zijn de stappen die betrokken zijn bij het programmeren van deze CPLD:

1. Ontwerpinvoer: Begin met het gebruik van een hardwarebeschrijving Language (HDL) zoals VHDL of Verilog, of een grafisch schema -opnametool om uw digitale logische ontwerp te maken.Deze eerste stap legt de basis voor de functionaliteit die u in de CPLD wilt implementeren.Gebruik ontwerpsoftware compatibel met de Max 7000 -serie, zoals Altera's Quartus II of Max+Plus II, die hulpmiddelen biedt voor het coderen, compileren en simuleren van uw ontwerp.

2. Compilatie en simulatie: Samen met uw ontwerp om de HDL -code of het schema te vertalen in een binair formaat dat de CPLD kan uitvoeren.Deze stap controleert ook op eventuele syntaxisfouten en zorgt ervoor dat de logica voldoet aan de ontwerpvereisten.Simuleren het gecompileerde ontwerp om de functionaliteit ervan te valideren.Dit omvat het uitvoeren van testgevallen tegen het ontwerp om de logica en timing ervan te verifiëren, waardoor het zich gedraagt zoals verwacht voordat het op het fysieke apparaat wordt geprogrammeerd.

3. Hardware -instellingen programmeren: Sluit de EPM7160ELC84-15 aan op de juiste programmeerhardware.Dit kan inhouden dat het opzetten van een JTAG-interface met apparaten zoals de ByteblasterMV, MasterBlaster of USB-Blaster.Zorg ervoor dat de CPLD correct is aangedreven en in de juiste configuratiemodus ingesteld voor programmering, meestal met een 5.0 V -voeding.

4. Programmeerproces: Open de programmeersoftware (zoals Quartus II-programmeur) en configureer deze om de EPM7160ELC84-15 te herkennen via de JTAG-interface.Laad het juiste programmeerbestand (.pof of .sof) in de software.Deze bestanden bevatten de gecompileerde ontwerpgegevens die nodig zijn om de CPLD te configureren.Voer de opdracht programmeren uit in de software om het ontwerp naar de CPLD over te dragen.Controleer het proces voor eventuele fouten en bevestig succesvolle programmeeraflossing.

5. Verificatie: Zodra de programmering is voltooid, voert u een verificatieproces uit om ervoor te zorgen dat de CPLD correct werkt binnen de beoogde toepassing.Dit kan het uitvoeren van grenstests of functionaliteitstests omvatten binnen het werkelijke systeem waar de CPLD wordt geïmplementeerd.Controleer of alle functionaliteiten worden uitgevoerd zoals ontworpen en dat het apparaat correct interageert met andere componenten in het systeem.

EPM7160ELC84-15 Voordelen

Kosteneffectiviteit

De EPM7160ELC84-15 is een kosteneffectieve oplossing voor het nodig hebben van complexe logische mogelijkheden zonder het hoge prijskaartje geassocieerd met nieuwere CPLD's of FPGA's.Dit maakt het aantrekkelijk voor budgetgevoelige projecten en voor educatieve of kleinschalige industriële toepassingen.

Niet-vluchtige configuratie

Met behulp van EEPROM-technologie behoudt de EPM7160ELC84-15 zijn geprogrammeerde configuratie, zelfs wanneer de stroom wordt uitgeschakeld.Deze niet-vluchtigheid zorgt voor de betrouwbaarheid van het apparaat en de consistentie in prestaties over stroomcycli, waardoor de noodzaak van externe niet-vluchtige geheugencomponenten wordt geëlimineerd.

Breed werkspanningsbereik

Het apparaat ondersteunt een breed bedieningsspanningsbereik van 4,75 V tot 5,25 V, dat verschillende voedingen biedt en zorgt voor compatibiliteit met zowel oudere als nieuwere systeemontwerpen.Deze veelzijdigheid is gunstig in omgevingen met gemengde spanning waar systeemcomponenten mogelijk niet dezelfde standaardspanningsniveaus delen.

Betrouwbare prestaties

Het apparaat biedt betrouwbare prestaties met een voortplantingsvertraging van 15 ns en ondersteuning voor bedrijfsfrequenties tot 100 MHz.Dit zorgt voor tijdige en efficiënte verwerking van logische bewerkingen, waardoor het geschikt is voor tijdgevoelige toepassingen in telecommunicatie, automotive-elektronica en industriële besturingssystemen.

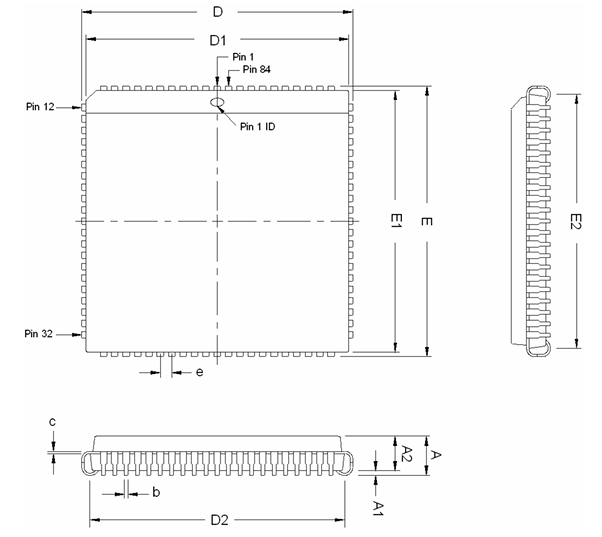

EPM7160ELC84-15 Verpakkingsafmetingen

Pakketoverzicht Dimensietabel

|

Symbool |

Inches |

||

|

Min. |

Nom. |

Max. |

|

|

A |

0,165 |

0.172 |

0,18 |

|

A1 |

0,02 |

- |

- |

|

A2 |

0.150 typ |

||

|

D |

1.185 |

1.190 |

1.195 |

|

D1 |

1.150 |

1.154 |

1.158 |

|

D2 |

1.082 |

1.110 |

1.138 |

|

E |

1.185 |

1.190 |

1.195 |

|

E1 |

1.150 |

1.154 |

1.158 |

|

E2 |

1.082 |

1.110 |

1.138 |

|

B |

0,013 |

- |

0,021 |

|

C |

0.008 TYP |

||

|

e |

0,050 typ |

||

Pakketoverzicht

EPM7160ELC84-15 fabrikant

De EPM7160ELC84-15 wordt vervaardigd door Intel Corporation, een wereldleider in halfgeleidertechnologie.Oorspronkelijk ontwikkeld door Altera, werd deze CPLD onderdeel van de productportfolio van Intel na de overname van Altera in 2015. Sindsdien is Intel de Max 7000-serie blijven ondersteunen, inclusief de EPM7160ELC84-15, onder zijn programmeerbare oplossingsgroep.Het rentmeesterschap van Intel zorgt ervoor dat het apparaat profiteert van hun geavanceerde productienormen, betrouwbaarheid op lange termijn en ondersteuning voor documentatie.Hoewel nu geclassificeerd als verouderd, blijft Intel's erfenis in programmeerbare logische apparaten zoals de EPM7160ELC84-15 wereldwijd dienen in legacy-systemen en gespecialiseerde toepassingen.

Conclusie

De EPM7160ELC84-15 staat als een zeer capabele CPLD op maat voor ingenieurs en systeemontwerpers die op zoek zijn naar kosteneffectieve logische integratie met flexibele programmeerbaarheid.Het op EEPROM gebaseerde geheugen, snelle voortplantingsvertraging en compatibiliteit met meerdere spanningsniveaus maken het sterk geschikt voor diverse elektronische omgevingen.Gesteund door Intel's productie -erfenis en gebouwd met functies zoals Multivolt I/O- en JTAG -compliance, blijft het apparaat ondanks zijn veroudering in oudere en gespecialiseerde systemen dienen.Of u nu werkt in industriële automatisering, ingebedde toepassingen of telecominfrastructuur, de EPM7160ELC84-15 levert betrouwbare prestaties en langetermijnwaarde.

Datasheet PDF

EPM7160ELC84-15 Datasheets:

Cilindrische batterijhouders.pdf

Over ons

ALLELCO LIMITED

Lees verder

Quick Inviry

Stuur een aanvraag, we zullen onmiddellijk reageren.

Veel Gestelde Vragen [FAQ]

1. Wat is het verschil tussen de EPM7160ELC84-15 en nieuwere CPLD's of FPGA's?

De EPM7160ELC84-15 is ideaal voor eenvoudiger of kostengevoelige toepassingen omdat het op EEPROM is gebaseerd en geen extern configuratiegeheugen vereist.Nieuwere CPLD's of FPGA's kunnen meer logische capaciteit, snellere prestaties of geavanceerde functies bieden, maar vaak tegen hogere kosten en complexiteit.Als uw ontwerp geen hoogwaardige bronnen nodig heeft, is dit apparaat een efficiëntere keuze.

2. Welke software heb ik nodig om de EPM7160ELC84-15 te programmeren?

U kunt Altera Max+Plus II of Intel Quartus II-software gebruiken om de EPM7160ELC84-15 te ontwerpen, compileren, simuleren en programmeren.Deze tools ondersteunen oudere Max 7000-serie CPLD's en bieden zowel schematische als op HDL gebaseerde ontwerpopties.

3. Hoe vaak kan ik de EPM7160ELC84-15 herprogrammeren?

De EPM7160ELC84-15 kan tot 100 keer worden herprogrammeerd dankzij zijn EEPROM-technologie.Dit zorgt voor updates en aanpassingen tijdens prototyping en zelfs na de implementatie, en biedt flexibiliteit op lange termijn.

4. Ondersteunt de EPM7160ELC84-15 gemengde spanningslogica-niveaus?

Ja, het ondersteunt Multivolt ™ I/O, wat betekent dat het kan communiceren met apparaten die werken op 5V, 3,3V of zelfs 2,5 V, waardoor het zich kan aanpassen aan verschillende spanningsomgevingen en het helpt om te integreren in systemen met gemengde technologie.

5. Kan ik een USB-blaster gebruiken voor het programmeren van deze CPLD?

Ja, USB-BLASTER, BYTEBLASTERMV en MASTERBLASTER zijn compatibele programmeerhulpmiddelen die via JTAG verbinding maken met de EPM7160ELC84-15 voor in-system programmering (ISP).

Wat u moet weten over de AD9984AKSTZ-170

Op 2025/04/18

Welke condensatoren doen in elektronische circuits

Op 2025/04/17

Populaire berichten

-

Complexe instructieset computers: hoe ze de computer hebben gewijzigd?

Op 8000/04/18 147774

-

USB-C-pinout en functies

Op 2000/04/18 112017

-

Met behulp van Xilinx Unified Simulation Primitives: een uitgebreide gids voor FPGA -ontwerp en simulatie

Op 1600/04/18 111351

-

Voedingsspanningen in elektronica: betekenis van VCC, VDD, VEE, VSS en GND

Op 0400/04/18 83771

-

RJ45 -connectorhandleiding: pinout, bedrading, kabeltypen en gebruik

Op 1970/01/1 79568

-

De ultieme gids voor draadkleurcodes in moderne elektrische systemen

De manier waarop onze elektrische systemen kleuren gebruiken, is niet alleen voor uiterlijk.Elke draadkleur geeft nu een specifieke functie aan, waardoor het gemakkelijker wordt om elektrische comp...Op 1970/01/1 66961

-

PURGE VLEP GIDS: Functie, symptomen, testen en vervanging voor optimale motorprestaties

De Purge -klep is een belangrijk onderdeel van het systeem van een auto dat helpt de lucht schoon te houden door brandstofdampen te beheren voordat ze in de atmosfeer kunnen ontsnappen.Dit helpt ni...Op 1970/01/1 63102

-

Kwaliteit (Q) Factor: vergelijkingen en toepassingen

De kwaliteitsfactor, of 'Q', is belangrijk bij het controleren hoe goed inductoren en resonatoren werken in elektronische systemen die radiofrequenties gebruiken (RF).'Q' meet hoe goed een circuit ...Op 1970/01/1 63041

-

Piekprestaties bereiken met de maximale stelling van de stroomoverdracht

De maximale stelling van de stroomoverdracht legt uit hoe energie van een bron, zoals een batterij of generator, naar een aangesloten belasting stroomt.Het toont de exacte voorwaarde waar de belast...Op 1970/01/1 54097

-

A23 Batterijspecificaties en compatibiliteit

De A23-batterij is een kleine, cilindervormige batterij met hoge spanning.Ook wel 23A, 23ae of MN21 genoemd, het loopt op 12 volt en veel hoger dan AA- of AAA -batterijen.Het speciale ontw...Op 1970/01/1 52185