Uitgebreide gids voor testbanken: tools en technieken voor digitale systeemverificatie

Deze gids onderzoekt TestBenches, een belangrijk hulpmiddel voor software -validatie die de voorwaarden simuleert om ingangen te testen en uitvoer te verifiëren.Testbanden spelen een rol bij het vroeg in ontwikkeling van bugs, waardoor softwarebetrouwbaarheid wordt verbeterd.Met praktische voorbeelden en inzichten benadrukt dit artikel hun gebruik, technieken en belang bij het bouwen van sterke, efficiënte digitale systemen.Catalogus

De rol van testbanden bij digitale systeemvalidatie

Een testbank is een component in het proces van digitale systeemvalidatie.Het is niet alleen een hulpmiddel voor het genereren van inputs en het verifiëren van uitgangen, het dient als een uitgebreid raamwerk dat de voorwaarden simuleert om de betrouwbaarheid, functionaliteit en gedrag van digitale systemen te beoordelen voordat ze in het veld worden ingezet.Door gecontroleerde omgevingen te creëren naar stress-testsystemen met een breed scala aan invoerscenario's, helpen testbanden u om potentiële ontwerpfouten vroeg in de ontwikkelingslevenscyclus te identificeren, lang voordat het systeem in productie wordt gebracht.Deze vroege detectie van bugs en kwetsbaarheden is nodig voor het verminderen van dure fouten, het waarborgen van de naleving van de prestatiespecificaties en het verbeteren van de algehele systeembetrouwbaarheid.

Naast het verifiëren van de juistheid van de antwoorden van het systeem, spelen testbanden een rol bij het beoordelen van randgevallen, timingproblemen en foutafhandelingsmechanismen, waardoor het systeem correct kan werken, zelfs onder extreme of onverwachte omstandigheden.Door geautomatiseerde testen en simulatie dragen testbanden bij aan hogere softwarekwaliteit, verbeterde prestaties en kortere ontwikkelingscycli door iteratieve testen mogelijk te maken zonder handmatige interventie.Ze dienen als een bescherming tegen mislukkingen die kunnen optreden na de inzet, waardoor de robuustheid en betrouwbaarheid van digitale systemen wordt gewaarborgd.

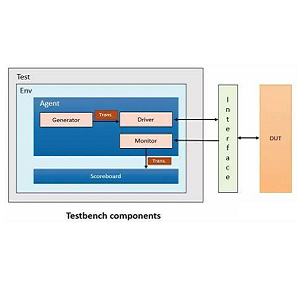

Belangrijke componenten van een testbank en hun functies

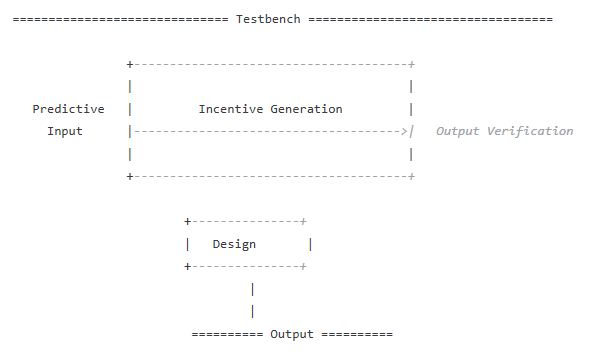

Om beter te begrijpen hoe testbanden werken, is het belangrijk om de componenten te verkennen die ze effectief maken.Een goed gemaakte testbench werkt door twee kerntaken te beheren: het genereren van inputs (stimuli) en het verifiëren van outputs.Laten we elke component in detail onderzoeken.

Stimulusgeneratie

Stimulusgeneratie omvat het creëren van een set inputsignalen die voorwaarden simuleren om het gedrag van een digitaal systeem te testen.Deze inputs moeten zowel nauwkeurig als realistisch zijn om ervoor te zorgen dat het systeem wordt onderworpen aan verschillende scenario's die het in de praktijk zou kunnen tegenkomen.Beschouw een basis RAM -module als een voorbeeld.De TestBench moet specifieke ingangen aan de module leveren en de uitgangen waarnemen om ervoor te zorgen dat deze zich gedraagt zoals verwacht.De belangrijkste ingangen voor een RAM -module omvatten meestal:

• CLK (klok): drijft de timing van het systeem aan.

• ADDR (adres): Geeft aan welke gegevenslocatie moet worden toegankelijk.

• Wen (schrijven Enable): bepaalt of gegevens naar het geheugen worden geschreven.

• Gegevens: de werkelijke informatie die naar de module wordt geschreven.

De uitvoer, bekend als dataout, vertegenwoordigt het resultaat van de interne bewerkingen van de module.Door zorgvuldig te scripten hoe deze inputs worden geleverd en gegevens worden bewaakt, kunt u controleren of het systeem correct uitvoert onder verschillende scenario's.Denk aan stimulusgeneratie als het opzetten van een testscenario in een laboratorium.Net zoals wetenschappers zorgvuldig de omstandigheden regelen om chemische reacties te observeren, maken digitale ontwerpers precieze inputs om te observeren hoe een systeem reageert.

Uitgangsverificatie

Uitgangsverificatie is het proces van controleren dat de werkelijke uitgangen van het systeem overeenkomen met de verwachte resultaten.Deze stap is van cruciaal belang om vroeg fouten te vangen voordat ze evolueren naar grotere problemen.Anderen gebruiken uitvoerverificatie om te bevestigen dat het systeem voldoet aan zijn beoogde functionaliteit en consequent presteert onder verschillende omstandigheden.Uitvoerverificatie omvat zowel geautomatiseerde als handmatige controles.Bijvoorbeeld:

• Geautomatiseerde verificatiehulpmiddelen: tools zoals ModellenIM en Quartus zorgen voor geautomatiseerde testen, waarbij de systeemuitgangen worden vergeleken met verwachte resultaten.Dit versnelt het verificatieproces en vermindert de fout.

• Handmatige verificatie (optioneel): voor meer complexe scenario's kunnen handmatige controles nodig zijn om ervoor te zorgen dat specifieke randgevallen worden behandeld.

Tools en technieken voor de implementatie van TestBench

Quartus: visuele invoer/uitvoersimulatie

Quartus biedt een grafische interface die invoer visueel rangschikt en uitvoer waarneemt.Deze methode kan gunstig zijn voor beginners of voor systemen die een meer hands-on, visuele aanpak vereisen.Door mogelijk te maken met een simulatie via een grafische omgeving, helpt Quartus de relatie tussen inputs en uitgangen te demystificeren, waardoor het gemakkelijker wordt om te begrijpen hoe een digitaal systeem zich in de tijd gedraagt.Een van de belangrijkste sterke punten van Quartus is dat het ideaal is voor beginners.De intuïtieve, visuele interface biedt een eenvoudige manier om te zien hoe inputs de uitgangen beïnvloeden zonder de noodzaak van uitgebreide script- of programmeerkennis.De feedback die het biedt helpt het gedrag van circuits gemakkelijker te begrijpen, waardoor het een nuttig hulpmiddel is voor degenen die nieuw zijn bij het ontwerp van het digitale systeem.Quartus heeft echter zijn beperkingen.Het opzetten van simulaties in Quartus kan tijdrovend zijn, met name voor complexere ontwerpen.De tool is minder flexibel in vergelijking met op script gebaseerde simulatietools, die meer aanpassings- en automatiseringsopties kunnen bieden.Voor het werken aan grootschalige of zeer gedetailleerde systemen kan dit gebrek aan flexibiliteit een uitdaging vormen.

ModellenIM: tekstgebaseerde simulatie met behulp van scripting

ModelsIM hanteert een andere benadering van simulatie door prioriteit te geven aan tekstgebaseerde input door scripting.Maak testscenario's met behulp van Verilog (.v) of VHDL (.vhd) scripts in plaats van het visueel rangschikken van ingangen en uitgangen.Deze methode biedt meer precisie en controle.In plaats van te vertrouwen op een grafische interface, definieert u hoe het systeem moet worden getest door gedetailleerde scripts, waardoor een grotere aanpassing en automatisering in het simulatieproces mogelijk is.Een van de belangrijkste sterke punten van ModelsIM is de flexibiliteit die het biedt.Door scripts te gebruiken, hebt u meer controle over testscenario's, zodat ze complexe en precieze simulaties kunnen maken.Zodra een ontwerper bekend is met de syntaxis en workflow, kan het instellen van simulaties veel sneller zijn in vergelijking met het gebruik van grafische hulpmiddelen zoals Quartus.De mogelijkheid om scripts opnieuw te gebruiken en te wijzigen draagt ook bij aan de efficiëntie ervan, met name in grotere projecten.De tekstgebaseerde benadering van ModelsIM heeft echter bepaalde beperkingen.Het vereist een goed begrip van Verilog- of VHDL -syntaxis, die een uitdaging kan vormen voor beginners die onbekend zijn met hardwarebeschrijving -talen.Als gevolg hiervan heeft ModelsIM een steilere leercurve in vergelijking met meer visuele simulatietools.Nieuwe gebruikers vinden het misschien moeilijk om aan de slag te gaan, maar met de praktijk kan de precisie en flexibiliteit die scripting wordt aangeboden een waardevol bezit worden.

Overbruggende theorie en praktijk in verificatie

Testbanden dienen als een brug tussen theoretische ontwerpen en toepassingen door te simuleren hoe een digitaal systeem zich zal gedragen onder verschillende omstandigheden, waaronder randgevallen en onverwachte ingangen.In digitaal ontwerp is het vaak moeilijk om te voorspellen hoe een systeem in de praktijk uitsluitend zal presteren op basis van theoretische modellen.Testbanden sluiten deze kloof door u toe te staan verder te gaan dan abstracte ontwerpconcepten en het gedrag van een systeem te evalueren in een gecontroleerde, gesimuleerde omgeving.Een van de belangrijkste voordelen van het gebruik van simulatietools in testbanden is de onmiddellijke feedback die ze geven tijdens foutopsporing.Tools zoals Multisim of ModelsIM bieden visuele representaties van systeemgedrag, waaruit blijkt hoe veranderingen in inputs in de loop van de tijd beïnvloeden.Met deze feedback kunt u problemen sneller vaststellen, fouten sporen terug naar hun oorzaak en hun ontwerpen dienovereenkomstig aanpassen.Als een systeem bijvoorbeeld niet voldoet aan de timingbeperkingen of onverwacht gedrag vertoont onder bepaalde inputsequenties, kan een testbench deze fouten onmiddellijk benadrukken, lang voordat het systeem fysiek wordt gebouwd.Door problemen in het begin van de ontwerpcyclus te identificeren, verminderen testbanden de behoefte aan kostbaar bewerkingen en fysieke prototyping, waardoor het verificatieproces wordt gestroomlijnd.Deze validatie in een vroeg stadium helpt ervoor te zorgen dat digitale systemen zowel functioneel correct als veerkrachtig zijn voor de omstandigheden, waardoor ze betrouwbaarder worden en het faalrisico na de implementatie verminderen.Op deze manier fungeren testbanden als een praktisch hulpmiddel voor het transformeren van theoretische ontwerpen in robuust.

Geavanceerde testbench -architectuur

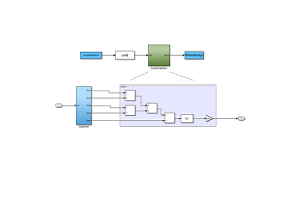

Geavanceerde testbanken gaan verder dan eenvoudige input-output testen door extra componenten op te nemen om complexe systemen te beheren.Een standaard testbench bevat drie belangrijke onderdelen: a Stimulusgenerator Om invoersignalen te maken, a Ontwerp onder testen (DUT), dat is de werkelijke hardware die wordt getest, en een Outputmonitor Dat controleert de output tegen de verwachte resultaten.Deze componenten werken samen om een krachtiger en nauwkeurige verificatie van digitale ontwerpen te garanderen.

Het verbeteren van de nauwkeurigheid van de testbench omvat het gebruik van technieken die ervoor zorgen dat een ontwerp betrouwbaar in verschillende scenario's presteert. Gerandomiseerde tests Introduceert onvoorspelbare invoerpatronen om de stabiliteit van het systeem onder verschillende omstandigheden te verifiëren. Edge Case Testing Richt zich op grensituaties waar het systeem het meest waarschijnlijk fouten tegenkomt.Ten slotte, Regressietest omvat heruitlopende tests na wijzigingen om te bevestigen dat er geen nieuwe problemen zijn geïntroduceerd, waardoor het systeem in de loop van de tijd consistent en foutloos blijft.

Scripttestbanken

Volg belangrijke best practices om efficiënte en betrouwbare testbanken in Verilog of VHDL te maken.Start eenvoudig, breid vervolgens uit door eerst de basisfunctionaliteit te testen en geleidelijk meer complexe scenario's toe te voegen.Gebruik opmerkingen en documentatie om uw scripts gemakkelijker te begrijpen en te onderhouden te maken door elke sectie duidelijk uit te leggen.Automatiseer ten slotte waar mogelijk om tijd te besparen en fouten te verminderen door lussen en functies te gebruiken om repetitieve taken en invoerpatronen aan te kunnen.

Over ons

ALLELCO LIMITED

Lees verder

Quick Inviry

Stuur een aanvraag, we zullen onmiddellijk reageren.

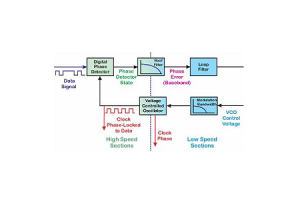

Digitale fase-vergrendelde lus (DPLL): ontwerp, componenten en bewerkingen

Op 2025/01/7

De evolutie en impact van RISC -architectuur in modern computergebruik

Op 2025/01/7

Populaire berichten

-

Complexe instructieset computers: hoe ze de computer hebben gewijzigd?

Op 8000/04/18 147778

-

USB-C-pinout en functies

Op 2000/04/18 112032

-

Met behulp van Xilinx Unified Simulation Primitives: een uitgebreide gids voor FPGA -ontwerp en simulatie

Op 1600/04/18 111351

-

Voedingsspanningen in elektronica: betekenis van VCC, VDD, VEE, VSS en GND

Op 0400/04/18 83788

-

RJ45 -connectorhandleiding: pinout, bedrading, kabeltypen en gebruik

Op 1970/01/1 79589

-

De ultieme gids voor draadkleurcodes in moderne elektrische systemen

De manier waarop onze elektrische systemen kleuren gebruiken, is niet alleen voor uiterlijk.Elke draadkleur geeft nu een specifieke functie aan, waardoor het gemakkelijker wordt om elektrische comp...Op 1970/01/1 66973

-

PURGE VLEP GIDS: Functie, symptomen, testen en vervanging voor optimale motorprestaties

De Purge -klep is een belangrijk onderdeel van het systeem van een auto dat helpt de lucht schoon te houden door brandstofdampen te beheren voordat ze in de atmosfeer kunnen ontsnappen.Dit helpt ni...Op 1970/01/1 63109

-

Kwaliteit (Q) Factor: vergelijkingen en toepassingen

De kwaliteitsfactor, of 'Q', is belangrijk bij het controleren hoe goed inductoren en resonatoren werken in elektronische systemen die radiofrequenties gebruiken (RF).'Q' meet hoe goed een circuit ...Op 1970/01/1 63043

-

Piekprestaties bereiken met de maximale stelling van de stroomoverdracht

De maximale stelling van de stroomoverdracht legt uit hoe energie van een bron, zoals een batterij of generator, naar een aangesloten belasting stroomt.Het toont de exacte voorwaarde waar de belast...Op 1970/01/1 54097

-

A23 Batterijspecificaties en compatibiliteit

De A23-batterij is een kleine, cilindervormige batterij met hoge spanning.Ook wel 23A, 23ae of MN21 genoemd, het loopt op 12 volt en veel hoger dan AA- of AAA -batterijen.Het speciale ontw...Op 1970/01/1 52195