XC2S50-5TQG144I FPGA: Functies, specificaties, toepassingen en programmeerhandleiding

De XC2S50-5TQG144I is een flexibele en krachtige FPGA (Field Programmable Gate Array) van AMD Xilinx's Spartan-II-familie.Het is ontworpen voor digitale projecten die aanpassing, snelheid en betrouwbaarheid nodig hebben.Deze gids legt de functies, specificaties, programmeerproces en gebruik van deze FPGA uit om u te helpen begrijpen hoe u er het beste van kunt maken.Catalogus

XC2S50-5TQG144I Overzicht

De XC2S50-5TQG144I is een Spartan-II FPGA van AMD Xilinx, ontworpen voor digitale projecten die flexibiliteit en prestaties nodig hebben.Het heeft 50.000 systeempoorten en 1.728 logische cellen, waardoor het complexe taken kan uitvoeren.De chip bevat 384 configureerbare logische blokken (CLB's) en 32.768 RAM -bits, waardoor het een goed geheugen- en verwerkingskracht krijgt.Met 92 ingang/uitvoer (I/O) -pennen kan het eenvoudig verbinding maken met andere componenten.Het wordt geleverd in een 144-pins dunne quad flat pack (TQFP), die compact en gemakkelijk te gebruiken is.De FPGA draait op 2,5 V (met een veilig bereik van 2.375V tot 2.625V) en werkt goed in temperaturen tussen -40 ° C en +100 ° C.Deze Spartan-II FPGA is gemaakt met 0,18-micron-technologie, waardoor het efficiënt en betrouwbaar is.Het is programmeerbaar, wat betekent dat u de functies indien nodig kunt bijwerken.

Voor een kosteneffectieve, krachtige oplossing is het plaatsen van een bulkorder bij ons de optimale keuze, die zorgt voor superieure kwaliteit.

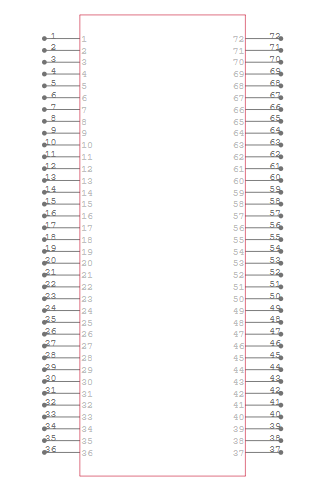

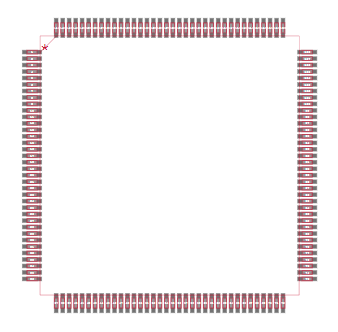

XC2S50-5TQG144I CAD-modellen

XC2S50-5TQG144I-symbool

XC2S50-5TQG144I FOESTRINT

XC2S50-5TQG144I 3D-model

XC2S50-5TQG144I Functies

• Systeempoorten: De XC2S50-5TQG144I FPGA biedt ongeveer 50.000 systeempoorten.Hierdoor kunnen het complexe digitale ontwerpen en toepassingen ondersteunen die een aanzienlijke hoeveelheid logische verwerkingsmogelijkheden vereisen.

• Logische cellen: Dit apparaat bevat 1.728 logische cellen, die de implementatie van ingewikkelde logische configuraties vergemakkelijken en verschillende digitale functionaliteiten binnen de FPGA maken.

• Configureerbare logische blokken (CLB's): Het beschikt over 384 configureerbare logische blokken (CLB's), die de basis biedt voor de logica van de FPGA.Deze blokken kunnen worden geprogrammeerd en opnieuw geconfigureerd om aan specifieke ontwerpvereisten te voldoen, waardoor de algehele veelzijdigheid van het apparaat wordt verbeterd.

• RAM: De FPGA is uitgerust met 32.768 bits interne RAM en biedt efficiënte gegevensopslag- en opzoekmogelijkheden voor taken met datamanipulatie en tijdelijke gegevensopslag.

• I/O -pinnen: Met 92 I/O-pinnen zorgt de XC2S50-5TQG144I voor voldoende externe connectiviteit, waardoor deze kan communiceren met andere apparaten en componenten in een systeem voor uitgebreide systeemintegratie.

• Werkspanning: Het apparaat werkt op een nominale spanning van 2,5 V, met een acceptabel bereik van 2.375V tot 2.625V.Dit spanningsbereik zorgt voor stabiele werking en betrouwbare prestaties onder verschillende elektrische omstandigheden.

• Temperatuurbereik: De XC2S50-5TQG144I is ontworpen om effectief te werken in een breed temperatuurbereik, van -40 ° C tot +100 ° C, waardoor het geschikt is voor implementatie in omgevingen met uitdagende thermische omstandigheden.

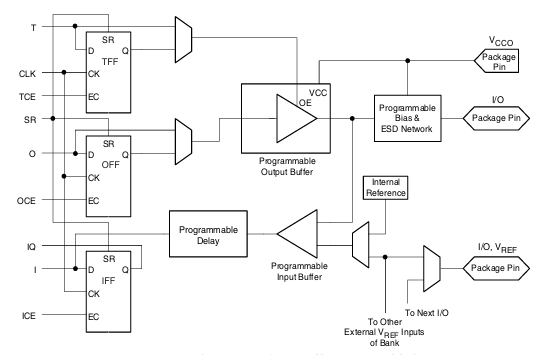

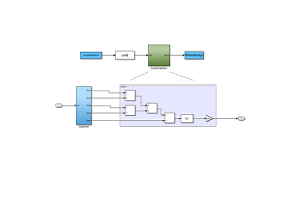

XC2S50-5TQG144I Blokdiagram

Het diagram laat zien hoe signalen in en uit de XC2S50-5TQG144I FPGA.Het legt uit hoe de chip input- en uitvoersignalen verwerkt om te communiceren met andere componenten.Op de outputzijde , Signalen komen van binnen de FPGA en gaan door opslageenheden die flip-flops worden genoemd.Deze flip-flops bevatten gegevens en zorgen ervoor dat signalen op het juiste moment veranderen.De signalen passeren vervolgens een programmeerbare uitgangsbuffer, waardoor het signaal is en bepaalt hoe snel het verandert.Er is ook een schakelaar (OE -besturing) die beslist of de uitgang actief moet zijn of uitgaat.Een beschermingscircuit voorkomt schade door statische elektriciteit voordat het signaal de I/O -pinnen bereikt, die verbinding maken met andere apparaten.Op de invoerzijde, Signalen van buitenaf gaan in via de programmeerbare invoerbuffer, die ze verwerkt voordat ze in de FPGA worden verzonden.Een programmeerbare vertragingseenheid helpt de signaaltiming aan te passen, zodat alles synchroon blijft.De FPGA kan ook een interne referentiespanning (VREF) gebruiken om verschillende spanningsniveaus te matchen, waardoor het gemakkelijker is om met verschillende soorten circuits te werken.Sommige I/O -pinnen delen deze spanningsreferentie om signalen stabiel te houden.Dit ontwerp helpt de FPGA signalen efficiënt te beheren, waardoor de juiste timing, bescherming en compatibiliteit met verschillende elektronische componenten wordt gewaarborgd.

XC2S50-5TQG144I Specificaties

|

Type |

Parameter |

|

Fabrikant |

AMD xilinx |

|

Serie |

Spartan®-II |

|

Verpakking |

Dienblad |

|

Onderdeelstatus |

Verouderd |

|

Aantal laboratorium/CLB's |

384 |

|

Aantal logische elementen/cellen |

1728 |

|

Totaal rambits |

32.768 |

|

Aantal I/O |

92 |

|

Aantal poorten |

50.000 |

|

Spanning - levering |

2.375V ~ 2.625V |

|

Montagetype |

Oppervlaktemontage |

|

Bedrijfstemperatuur |

-40 ° C ~ 100 ° C (TJ) |

|

Pakket / kast |

144-lqfp |

|

Leverancierapparaatpakket |

144-tqfp (20x20) |

|

Base Productnummer |

XC2S50 |

XC2S50-5TQG144I TOEPASSINGEN

Ingebedde systemen

In ingebedde systemen biedt de XC2S50-5TQG144I de nodige logica voor op microcontroller gebaseerde toepassingen.Het wordt uitgebreid gebruikt in auto-elektronica, draagbare apparaten en kleinschalige robotica om de functionaliteit en responsiviteit te verbeteren.

Signaalverwerking

De FPGA blinkt uit in signaalverwerkingstaken, waarbij het vermogen om parallelle verwerking uit te voeren vereist is.Het is ideaal voor audio- en video-verwerking, telecommunicatie en data-analyse, die de pk biedt om complexe algoritmen en high-speed gegevensstromen te verwerken.

Industriële controlesystemen

Industriële controlesystemen profiteren van de robuustheid en programmeerbaarheid van deze FPGA, waardoor het geschikt is voor toepassingen zoals procescontrole, machineautomatisering en systeembewaking.De betrouwbaarheid ervan zorgt voor consistente prestaties in omgevingen die precisie en operationele stabiliteit vereisen.

Communicatiesystemen

In communicatiesystemen helpt de XC2S50-5TQG144I helpt bij het beheren van gegevensoverdracht en ontvangst, ondersteunende activiteiten zoals signaalmodulatie en demodulatie, protocolconversie en netwerkroutering.Het aanpassingsvermogen is van cruciaal belang in het evolueren van telecommunicatie -infrastructuren en opkomende draadloze technologieën.

Prototyping en ontwikkeling

De FPGA wordt ook uitgebreid gebruikt voor prototyping digitale circuits.Velen gebruiken het om hun ideeën te testen en te verfijnen vóór de definitieve productie, vooral in complexe ASIC- en aangepaste chip -ontwerpprojecten.Deze mogelijkheid vermindert de ontwikkelingstijd en -kosten en versnelt het pad van concept naar markt.

XC2S50-5TQG144I Vergelijkbare onderdelen

XC2S50-5TQG144i Voordelen

Kosteneffectiviteit

De XC2S50-5TQG144i onderscheidt zich voor zijn betaalbaarheid en levert meer functies per dollar dan veel concurrerende FPGA's.Deze kosteneffectiviteit wordt bereikt door geavanceerde procestechnologie en een efficiënte architectuur, waardoor een bredere implementatie op kostengevoelige markten mogelijk is.

High-performance I/O en verpakking

Deze FPGA ondersteunt een breed scala aan I/O-normen en is beschikbaar in verschillende kosteneffectieve verpakkingsopties.Deze functies zorgen ervoor dat het apparaat kan worden geïntegreerd in meerdere toepassingen zonder prestaties op te offeren, waardoor het ideaal is voor zowel hoogwaardige als volumegedreven markten waar interface-veelzijdigheid en fysieke beperkingen factoren zijn.

Systeemniveau-functies

Uitgerust met geavanceerde functies voor geheugenbeheer zoals gedistribueerd RAM en configureerbaar blok RAM, verbetert de XC2S50-5TQG144I de efficiëntie van gegevensverwerking.Deze functies vergemakkelijken complexe gegevensopslag- en verwerkingstaken, waardoor de algemene prestaties en schaalbaarheid van het systeem worden gestimuleerd.

Herprogrammeerbaarheid

De herprogrammeerbaarheid van de XC2S50-5TQG144I maakt onbeperkte wijzigingen mogelijk in de configuratie, wat gunstig is tijdens de ontwikkelingsfase.Deze flexibiliteit maakt het mogelijk om ontwerpen te verfijnen via iteratieve updates zonder extra hardwarekosten, het bevorderen van innovatie en het verkorten van de tijd tot eindproduct.

XC2S50-5TQG144I Programmeerstappen

Het programmeren van de XC2S50-5TQG144I FPGA uit de Spartan-II-serie van AMD Xilinx omvat een gestructureerde reeks stappen die zijn ontworpen om een digitaal ontwerp efficiënt te vertalen in een functionele FPGA-configuratie.Hier is een geïntegreerde en gedetailleerde gids om u te helpen door het programmeerproces:

1. Ontwerpinvoer

Begin met de ontwerpinvoerfase, waarbij u uw digitale logica maakt met behulp van een hardwarebeschrijving Language (HDL), zoals VHDL of Verilog.Deze eerste stap omvat het detailleren van de functionaliteit en logica die u in de FPGA wilt implementeren.Het is vereist dat uw ontwerp nauwkeurig is en nauwkeurig de beoogde bewerkingen vertegenwoordigt om succesvolle synthese en implementatie te garanderen.

2. Synthese

Gebruik in de synthese -stap een synthesetool om uw HDL -code om te zetten in een netlijst.Een netlijst is een uitsplitsing van uw ontwerp in een indeling met verschillende onderling verbonden logische elementen zoals poorten en flip-flops.Dit proces vertaalt uw theoretisch ontwerp in een praktische blauwdruk die de FPGA kan begrijpen en implementeren.

3. Implementatie

Implementatie omvat verschillende substappen: in kaart brengen, plaatsen en routeren.Mapping wijst de elementen van uw netlijst toe aan specifieke logische blokken binnen de FPGA.Plaatsing bepaalt de fysieke locaties van deze blokken op de FPGA -chip om de prestaties en het gebruik van middelen te optimaliseren.Routing verbindt deze blokken via de programmeerbare interconnectbronnen van de FPGA.Deze fase zorgt ervoor dat het ontwerp voldoet aan alle fysieke en prestatiebeperkingen.

4. Beperkingsdefinitie

Tijdens het ontwerpproces is het definiëren van beperkingen nodig.Beperkingen begeleiden de implementatiehulpmiddelen door vereisten zoals timing op te geven (hoe snel de FPGA zou moeten werken), en pin -toewijzingen (welke pinnen op de FPGA verbinding maken met verschillende delen van uw hardware).Deze zijn gearticuleerd in een gebruikersbeperkingsbestand (UCF), wat helpt bij het verfijnen van het ontwerp om aan specifieke operationele normen te voldoen.

5. Bitstream -generatie

Zodra uw ontwerp met succes de implementatiefase doorloopt, is de volgende stap het genereren van een bitstream -bestand.Dit bestand bevat alle configuratiegegevens die de FPGA nodig hebben om het ontwerp uit te voeren.De bitstream is de uiteindelijke uitvoer van het programmeerproces, die de volledige, geprogrammeerde status van de FPGA vertegenwoordigt.

6. Apparaatprogrammering

De laatste stap is om de bitstream in de XC2S50-5TQG144I FPGA te laden, die kan worden gedaan met behulp van verschillende configuratiemodi, afhankelijk van uw opstelling.In Master Seriële modus, de FPGA leest autonoom de configuratiegegevens van een bijgevoegd serieel prom (programmeerbaar alleen-lezen geheugen). Slaven seriële modus Hiermee kan een extern masterapparaat, zoals een microcontroller, de FPGA -configuratiegegevens serieel voeren. Slaven parallelle modus Schakelt snelle programmering in door configuratiegegevens parallel te leveren vanaf een extern masterapparaat.Ten slotte, Boundary Scan (JTAG) -modus Gebruikt de JTAG -interface voor zowel programmering als testen, waardoor het nuttig wordt tijdens de ontwikkeling voor iteratieve foutopsporing en verificatie.

XC2S50-5TQG144I PAKKACHTEN DIMENTIES

De XC2S50-5TQG144I is een veldprogrammeerbare poortarray (FPGA) van de familie Spartan-II van Xilinx, gehuisvest in een 144-pins dun quad flat pack (TQFP) pakket.Dit pakket meet 20 mm x 20 mm.

XC2S50-5TQG144I fabrikant

De XC2S50-5TQG144I is een FPGA uit de Spartan-II-familie, vervaardigd door AMD Xilinx.Xilinx, nu onderdeel van AMD, is een toonaangevend halfgeleiderbedrijf dat gespecialiseerd is in FPGA's, adaptieve SOC's en andere programmeerbare logische apparaten.De XC2S50-5TQG144I werd oorspronkelijk ontwikkeld onder de Xilinx Spartan-II-serie, met 50.000 systeempoorten en 1.728 logische cellen, ontworpen voor krachtige en toch kosteneffectieve toepassingen.Met de acquisitie van Xilinx door AMD blijft het bedrijf legacy-producten zoals de Spartan-II-serie ondersteunen terwijl het nieuwere FPGA-architecturen bevordert.De XC2S50-5TQG144I is echter een FPGA van oudere generatie en kan uiteindelijk worden geconfronteerd met een eventuele veroudering naarmate AMD Xilinx verschuift naar meer geavanceerde FPGA-families.

Conclusie

De XC2S50-5TQG144I FPGA is een kosteneffectieve en herprogrammeerbare chip die geweldige prestaties en flexibiliteit biedt.Het wordt veel gebruikt in ingebedde systemen, industriële machines en communicatienetwerken vanwege de snelle verwerking en sterke connectiviteitsopties.Met zijn vermogen om te worden geprogrammeerd en bijgewerkt, helpt deze FPGA helpt nieuwe ideeën te testen en te ontwikkelen vóór de definitieve productie.Hoewel nieuwere FPGA's beschikbaar zijn, blijft dit model een solide keuze voor projecten die een betrouwbare en betaalbare FPGA -oplossing nodig hebben.Deze gids biedt een duidelijk en eenvoudig overzicht van de functies, het gebruik en het programmeerproces van de FPGA, waardoor het voor iedereen een waardevolle bron is.

Over ons

ALLELCO LIMITED

Lees verder

Quick Inviry

Stuur een aanvraag, we zullen onmiddellijk reageren.

Veel Gestelde Vragen [FAQ]

1. Kan ik de XC2S50-5TQG144i gebruiken voor hogesnelheidstoepassingen?

De XC2S50-5TQG144I ondersteunt snelheden tot 200 MHz, waardoor het geschikt is voor de meeste ingebedde en industriële toepassingen.Als uw project echter high-speed interfaces zoals PCIE- of DDR-geheugen vereist, heeft u mogelijk een meer geavanceerde FPGA nodig zoals de Spartan-6- of Artix-7-serie.

2. Hoe verhoudt de XC2S50-5TQG144I zich tot de nieuwere Spartan-3 of Spartan-6 FPGAS?

Terwijl nieuwere FPGA's zoals Spartan-3 of Spartan-6 verbeterde prestaties, hogere logische dichtheid en extra functies bieden, blijft de XC2S50-5TQG144i een voorkeurskeuze voor kostengevoelige projecten met matige complexiteit.Als u legacy-compatibiliteit of een stabiele supply chain nodig heeft, is de XC2S50-5TQG144I een geweldige optie.

3. Welke programmeerhulpmiddelen zijn compatibel met de XC2S50-5TQG144I FPGA?

De XC2S50-5TQG144I is geprogrammeerd met Xilinx ISE (Integrated Software-omgeving).Terwijl nieuwere Xilinx-tools zoals Vivado de Spartan-II-familie niet ondersteunen, biedt ISE alle nodige ontwerp-, synthese- en programmeerfunctionaliteiten voor deze FPGA.

4. Kan ik een bestaand Spartan-II-ontwerp migreren naar een nieuwere FPGA?

Ja, maar het vereist aanpassingen.De nieuwere Spartan-3- en Spartan-6-families gebruiken verschillende architectuur, spanningsniveaus en configuratiemethoden.Als u migratie overweegt, kunnen we helpen bij het selecteren van geschikte alternatieven en het minimaliseren van ontwerpwijzigingen.

5. Ondersteunt de XC2S50-5TQG144i JTAG-programmering?

A: Ja, de FPGA ondersteunt JTAG (IEEE 1149.1) Boundary Scan -programmering, waardoor eenvoudige foutopsporing en configuratie mogelijk is met behulp van een standaard JTAG -interface.Dit is handig voor zowel initiële programmering als herconfiguratie zonder extern geheugen.

XC4013XL-3PQ240C FPGA: alternatieven, specificaties, applicaties en datasheet

Op 2025/03/18

RF -stroomversterkers: hoe ze werken, welk type is efficiënter is

Op 2025/03/18

Populaire berichten

-

Complexe instructieset computers: hoe ze de computer hebben gewijzigd?

Op 8000/04/18 147778

-

USB-C-pinout en functies

Op 2000/04/18 112032

-

Met behulp van Xilinx Unified Simulation Primitives: een uitgebreide gids voor FPGA -ontwerp en simulatie

Op 1600/04/18 111351

-

Voedingsspanningen in elektronica: betekenis van VCC, VDD, VEE, VSS en GND

Op 0400/04/18 83788

-

RJ45 -connectorhandleiding: pinout, bedrading, kabeltypen en gebruik

Op 1970/01/1 79589

-

De ultieme gids voor draadkleurcodes in moderne elektrische systemen

De manier waarop onze elektrische systemen kleuren gebruiken, is niet alleen voor uiterlijk.Elke draadkleur geeft nu een specifieke functie aan, waardoor het gemakkelijker wordt om elektrische comp...Op 1970/01/1 66973

-

PURGE VLEP GIDS: Functie, symptomen, testen en vervanging voor optimale motorprestaties

De Purge -klep is een belangrijk onderdeel van het systeem van een auto dat helpt de lucht schoon te houden door brandstofdampen te beheren voordat ze in de atmosfeer kunnen ontsnappen.Dit helpt ni...Op 1970/01/1 63109

-

Kwaliteit (Q) Factor: vergelijkingen en toepassingen

De kwaliteitsfactor, of 'Q', is belangrijk bij het controleren hoe goed inductoren en resonatoren werken in elektronische systemen die radiofrequenties gebruiken (RF).'Q' meet hoe goed een circuit ...Op 1970/01/1 63043

-

Piekprestaties bereiken met de maximale stelling van de stroomoverdracht

De maximale stelling van de stroomoverdracht legt uit hoe energie van een bron, zoals een batterij of generator, naar een aangesloten belasting stroomt.Het toont de exacte voorwaarde waar de belast...Op 1970/01/1 54097

-

A23 Batterijspecificaties en compatibiliteit

De A23-batterij is een kleine, cilindervormige batterij met hoge spanning.Ook wel 23A, 23ae of MN21 genoemd, het loopt op 12 volt en veel hoger dan AA- of AAA -batterijen.Het speciale ontw...Op 1970/01/1 52195