Wisbare programmeerbare logische apparaten (EPLDS): een handleiding voor ontwerp en toepassingen

Deze gids introduceert wistbare programmeerbare logische apparaten (EPLD's), een flexibele en herbruikbare technologie in geïntegreerde circuits.In tegenstelling tot traditionele programmeerbare apparaten, kunnen EPLD's meerdere keren opnieuw worden geconfigureerd, waardoor ze ideaal zijn voor het evolueren van ontwerpbehoeften.We zullen hun mogelijkheden, applicaties in industrieën zoals telecommunicatie en automotive verkennen, en belangrijke factoren waarmee deze moet worden overwogen bij het gebruik van deze veelzijdige apparaten in moderne elektronica.Catalogus

Overzicht

Wisbare programmeerbare logische apparaten (EPLD's), geïntroduceerd in het midden van de jaren tachtig door Aitera, bracht een revolutie teweeg in de programmeerbare logica met hun hoge integratiedichtheid en flexibiliteit, waarbij de mogelijkheden van vergelijkbare apparaten zoals generieke array-logica (GAL) overtreffen.EPLD's maken een breder bereik van logische functies mogelijk binnen een enkele chip, waardoor ze veelzijdig en efficiënt zijn voor verschillende toepassingen.Hun herprogrammeerbaarheid maakt het mogelijk om ontwerpen aan te passen zonder hardware te vervangen, een belangrijk voordeel in industrieën zoals telecommunicatie en automotive, waar snelle prototyping nodig is.Het compacte ontwerp van EPLD's en het lage stroomverbruik maken ze ideaal voor ingebedde systemen en draagbare apparaten, wat hun technische en praktische voordelen benadrukt in het moderne digitale logische ontwerp.

PLD -apparaatontwerpstappen

Het ontwerpen van een programmeerbaar logische apparaat (PLD) omvat verschillende stappen om een functioneel en efficiënt ontwerp te creëren.

Het proces begint met Het definiëren van de circuitlogische functies.Dit kan worden gedaan met behulp van schematische diagrammen of hardwarebeschrijving talen (HDL's).Schematische diagrammen bieden een eenvoudige manier om basislogische circuits te visualiseren, maar zijn minder effectief voor het afhandelen van complexe ontwerpen.HDL's bieden daarentegen een meer beknopte en flexibele manier om logische functies te beschrijven, waardoor ze de voorkeurskeuze zijn voor moderne PLD -ontwerpen.

Vervolgens kiezen ontwerpers een geschikte HDL voor hun project.Populaire opties zijn onder meer Abel, VHDL en Verilog.Abel is ideaal voor eenvoudigere ontwerpen, zoals tellers of encoders, omdat het Booleaanse vergelijkingen en waarheidstabellen gebruikt.VHDL is meer gestructureerd en blinkt uit in het omgaan met complexe logica, waardoor het geschikt is voor ingewikkelde projecten.Verilog, met zijn compacte, C-achtige syntaxis, is geweldig voor zowel logisch ontwerp als simulatie, waardoor het een veelzijdige optie is voor geavanceerde applicaties.De keuze van HDL hangt af van de complexiteit en specifieke vereisten van het project.

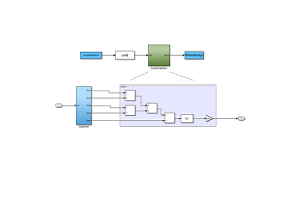

Zodra de logische functies zijn gedefinieerd, is de volgende stap programmeren en simulatie.Gespecialiseerde software compileert de beschreven logica en converteert deze in Booleaanse uitdrukkingen, die vervolgens worden opgeslagen als een Jedec (JEDC) -bestand.Voordat het ontwerp wordt overgebracht naar hardware, worden simulaties binnen de software uitgevoerd om te controleren of de logica functioneert zoals bedoeld.Deze simulatiefase is belangrijk, omdat het ervoor zorgt dat het ontwerp voldoet aan de prestaties van prestaties en de kans op fouten tijdens de implementatie vermindert.

Eindelijk is het ontwerp gedownload naar het PLD -apparaat.Dit omvat het overbrengen van het JEDEC -bestand naar de hardware met behulp van een programmeur, een apparaat dat specifiek is ontworpen om het bestand te schrijven in PLD's zoals PROMS, EEPROMS, GALS, CPLDS of PALS.Programmeurs maken verbinding met een computer via een parallelle poort en laden het ontwerp nauwkeurig op de hardware.Deze stap voltooit het proces en transformeert het ontwerp van een digitaal model in een fysiek, functionerend apparaat.

Het PLD -ontwerpproces omvat vier hoofdstappen: het definiëren van de logische functies, het kiezen van een geschikte HDL, programmeren en simuleren van het ontwerp en het downloaden van het uiteindelijke ontwerp naar de hardware.Elke fase speelt een rol bij het waarborgen van het succes en de betrouwbaarheid van het apparaat.Naarmate hulpmiddelen en methoden blijven evolueren, worden PLD -ontwerpen flexibeler, efficiënter en in staat om steeds complexere toepassingen te verwerken.

Over ons

ALLELCO LIMITED

Lees verder

Quick Inviry

Stuur een aanvraag, we zullen onmiddellijk reageren.

Complexe instructieset computers: hoe ze de computer hebben gewijzigd?

Op 2024/12/30

Het verkennen van de veelzijdigheid van MP (Microprocessor) -technologie

Op 2024/12/30

Populaire berichten

-

Complexe instructieset computers: hoe ze de computer hebben gewijzigd?

Op 8000/04/18 147757

-

USB-C-pinout en functies

Op 2000/04/18 111934

-

Met behulp van Xilinx Unified Simulation Primitives: een uitgebreide gids voor FPGA -ontwerp en simulatie

Op 1600/04/18 111349

-

Voedingsspanningen in elektronica: betekenis van VCC, VDD, VEE, VSS en GND

Op 0400/04/18 83719

-

RJ45 -connectorhandleiding: pinout, bedrading, kabeltypen en gebruik

Op 1970/01/1 79508

-

De ultieme gids voor draadkleurcodes in moderne elektrische systemen

De manier waarop onze elektrische systemen kleuren gebruiken, is niet alleen voor uiterlijk.Elke draadkleur geeft nu een specifieke functie aan, waardoor het gemakkelijker wordt om elektrische comp...Op 1970/01/1 66894

-

Kwaliteit (Q) Factor: vergelijkingen en toepassingen

De kwaliteitsfactor, of 'Q', is belangrijk bij het controleren hoe goed inductoren en resonatoren werken in elektronische systemen die radiofrequenties gebruiken (RF).'Q' meet hoe goed een circuit ...Op 1970/01/1 63010

-

PURGE VLEP GIDS: Functie, symptomen, testen en vervanging voor optimale motorprestaties

De Purge -klep is een belangrijk onderdeel van het systeem van een auto dat helpt de lucht schoon te houden door brandstofdampen te beheren voordat ze in de atmosfeer kunnen ontsnappen.Dit helpt ni...Op 1970/01/1 62998

-

Piekprestaties bereiken met de maximale stelling van de stroomoverdracht

De maximale stelling van de stroomoverdracht legt uit hoe energie van een bron, zoals een batterij of generator, naar een aangesloten belasting stroomt.Het toont de exacte voorwaarde waar de belast...Op 1970/01/1 54081

-

A23 Batterijspecificaties en compatibiliteit

De A23-batterij is een kleine, cilindervormige batterij met hoge spanning.Ook wel 23A, 23ae of MN21 genoemd, het loopt op 12 volt en veel hoger dan AA- of AAA -batterijen.Het speciale ontw...Op 1970/01/1 52115