EPM7064Stc100-7 CPLD: Functies, toepassingen en programmeergids in systemen

De EPM7064STC100-7 is een krachtige chip uit Intel's Max® 7000S-serie, ontworpen om complexe taken in elektronische apparaten aan te kunnen.Deze gids bespreekt de belangrijkste kenmerken en toepassingen van de EPM7064STC100-7, en benadrukt het vermogen om gemakkelijk te worden herprogrammeerd, de snelle werking en het flexibele ontwerp.Ideaal voor veel verschillende technologieën, van kleine gadgets tot grote industriële machines, deze chip is een belangrijk stuk voor het bouwen van geavanceerde digitale circuits.Catalogus

EPM7064STC100-7 Beschrijving

De EPM7064STC100-7 is een complex programmeerbaar logisch apparaat (CPLD) uit de Max® 7000 -serie van Intel.Het heeft 64 macrocellen en 1.250 poorten, die helpen bij het bouwen van complexe digitale circuits.Deze chip loopt met een maximale snelheid van 166,7 MHz, met een signaalvertraging van 7,5 nanoseconden (NS).Het heeft 68 invoer/uitvoer (I/O) -pennen die werken met 3,3V en 5V -logica, waardoor het gemakkelijk te gebruiken is in verschillende circuits.Een belangrijke functie is de programmeerbaarheid van 5.0V in-system (ISP) via een JTAG-interface (IEEE 1149.1).Dit betekent dat u het opnieuw kunt programmeren zonder het uit het circuit te verwijderen, waardoor testen en updates gemakkelijker worden.Het wordt geleverd in een 100-pins dunne quad flat pack (TQFP), een compact pakket voor oppervlakken.Deze CPLD wordt gebruikt in ingebedde systemen, digitale signaalverwerking, communicatieapparaten en industriële automatisering.

We bieden hoogwaardige componenten en aangepaste services, dus het is het beste om uw bulkorder bij ons te plaatsen voor betrouwbare CPLD-oplossingen.

EPM7064STC100-7 Functies

• Logica met hoge dichtheid: De EPM7064STC100-7 is ontworpen met 64 macrocellen en 1.250 bruikbare poorten, waardoor het zeer geschikt is voor het implementeren van complexe logische functies in digitale circuits.Deze architectuur met hoge dichtheid maakt het mogelijk om ingewikkelde logische ontwerpen te maken met behoud van de efficiëntie in programmeerbare logische bewerkingen.De goed geoptimaliseerde macrocell-structuur zorgt voor een effectief gebruik van beschikbare bronnen, ter ondersteuning van geavanceerde combinatie- en sequentiële logische implementaties.

• Snelle prestaties: Gebouwd voor snelle verwerking, werkt de EPM7064Stc100-7 met een maximale interne frequentie van 166,7 MHz, waardoor een snelle uitvoering van logische functies mogelijk is.De voortplantingsvertraging van 7,5 ns zorgt voor minimale latentie.Deze snelle schakelcapaciteit verbetert het vermogen van het apparaat om snelle gegevensverwerking, signaalconditionering en besturingstaken efficiënt af te handelen, waardoor het een betrouwbare keuze is voor veeleisende digitale systemen.

• Veelzijdige I/O: Met 68 programmeerbare ingang/uitgangspinnen biedt de EPM7064STC100-7 een uitzonderlijke flexibiliteit voor integratie in verschillende circuitontwerpen.Ter ondersteuning van zowel 3,3 V- als 5V -logische niveaus, maakt het naadloze compatibiliteit met verschillende systeemspanningen mogelijk, waardoor de behoefte aan extra spanningsniveau -shifters wordt geëlimineerd.Dit aanpassingsvermogen maakt het goed geschikt voor toepassingen in omgevingen met gemengde spanning, waardoor brede toepasbaarheid wordt gewaarborgd in ingebedde systemen, industriële bedieningselementen en communicatienetwerken.

• System-programmeerbaarheid (ISP): Een van de voordelen van de EPM7064Stc100-7 is de programmeerbaarheid van 5.0V in-system (ISP), gefaciliteerd via een IEEE STD.1149.1 JTAG -interface.Met deze functie kunnen logische functies herprogrammeren en wijzigen zonder het apparaat te verwijderen of fysiek te verwijderen, onderhoud, foutopsporing en iteratieve ontwikkeling te vereenvoudigen.De ISP -mogelijkheid vermindert downtime en verbetert de flexibiliteit van firmware -updates, waardoor het van onschatbare waarde is voor dynamische en herconfigureerbare digitale ontwerpen.

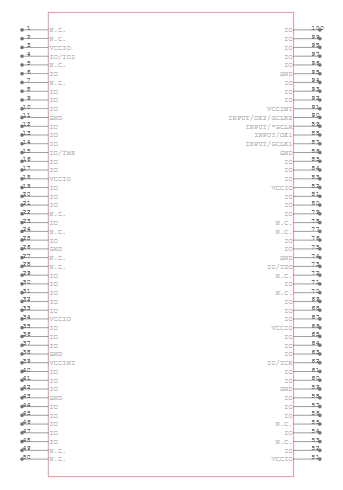

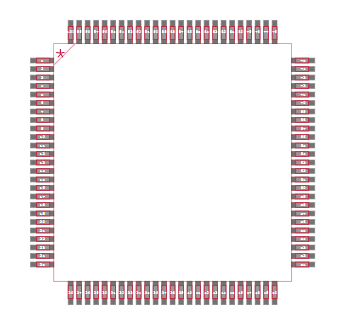

EPM7064STC100-7 CAD-modellen

EPM7064STC100-7 Symbool

Voetafdruk

EPM7064STC100-7 3D-model

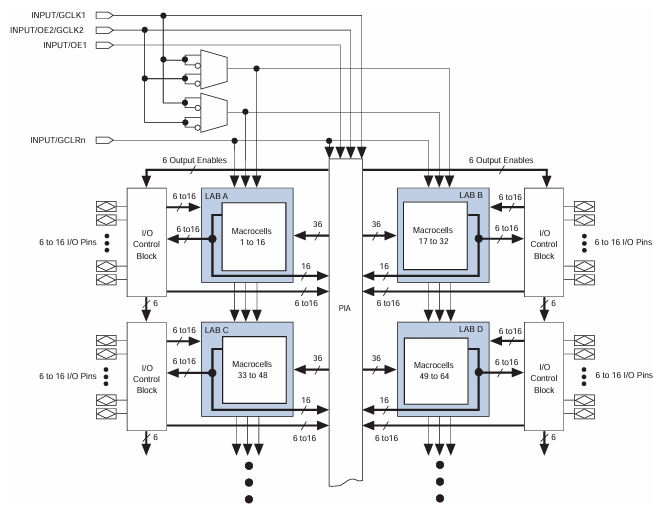

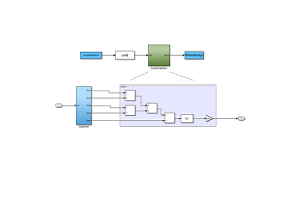

Blokdiagram

De Blokdiagram laat zien hoe de logische elementen van de chip zijn verbonden en gecontroleerd.Het heeft vier logische arrayblokken (labs), gelabeld A, B, C en D, die elk 16 macrocellen bevatten.Deze macrocellen voeren logische functies uit en ze maken verbinding via een programmeerbare interconnectarray (PIA), die flexibele routing van signalen mogelijk maakt.Elk lab is gekoppeld aan een I/O -besturingsblok, dat maximaal 16 ingang/uitgangspinnen per laboratorium hanteert.Het diagram toont ook globale besturingssignalen (GCLK1, GCLK2, OE1 en GCLRN) die helpen bij het beheren van klokken en resetten voor de chip.Sommige logische poorten verwerken deze signalen voordat ze verschillende delen van het systeem bereiken.Het ontwerp van de EPM7064Stc100-7 maakt het mogelijk om te worden gebruikt in verschillende programmeerbare logische toepassingen, zoals statusmachines, adresdecodering en andere aangepaste digitale circuits.De flexibele onderlinge verbindingen zorgen voor een efficiënte signaalstroom en betrouwbare werking.

EPM7064STC100-7 Specificaties

|

Type |

Parameter |

|

Fabrikant |

Altera/intel |

|

Serie |

Max® 7000s |

|

Verpakking |

Dienblad |

|

Onderdeelstatus |

Verouderd |

|

Programmeerbaar type |

In systeem programmeerbaar |

|

Vertragingstijd TPD (1) Max |

7.5 ns |

|

Spanningsvoorziening - Intern |

4.75V ~ 5.25V |

|

Aantal logische elementen/blokken |

4 |

|

Aantal macrocellen |

64 |

|

Aantal poorten |

1250 |

|

Aantal I/O |

68 |

|

Bedrijfstemperatuur |

0 ° C ~ 70 ° C (TA) |

|

Montagetype |

Oppervlaktemontage |

|

Pakket / kast |

100-tqfp |

|

Leverancierapparaatpakket |

100-tqfp (14x14) |

|

Base Productnummer |

EPM7064 |

EPM7064STC100-7 In-System Programming (ISP) -sequentie

De EPM7064Stc100-7, een deel van de Max 7000S CPLD-familie, volgt een zes-fasen in-system programmering (ISP) -sequentie om de juiste configuratie te garanderen.Met dit proces kunt u het apparaat programmeren zonder het uit de printplaat te verwijderen.Het ISP -proces omvat het verplaatsen van instructies, adressen en gegevens via de TDI (testgegevens in) pin terwijl het ophalen van antwoorden via de TDO (testgegevens uit) pin.

De eerste fase, Voer ISP in, zorgt ervoor dat de I/O -pins soepel overgaan van de gebruikersmodus naar de ISP -modus en ongeveer 1 ms vereist.Dit wordt gevolgd door Controleer ID, waarbij de silicium -ID van het apparaat wordt gelezen om het juiste doel te bevestigen.Vervolgens de Bulk wissen Stageverschuivingen in het wissen van instructies en passen een 100ms puls toe, waardoor alle bestaande gegevens in de EEPROM -cellen worden gewist.De Programma Stage volgt, waar adressen en gegevens achtereenvolgens in het apparaat worden verplaatst, waarbij programmeerpulsen worden toegepast om de EEPROM -cellen te configureren.Elk adres moet afzonderlijk worden geprogrammeerd, waardoor deze stap tijdrovend wordt, afhankelijk van het aantal EEPROM-cellen in het apparaat.

Zodra programmeren is voltooid, is de Verifiëren Stage zorgt ervoor dat gegevens correct zijn opgeslagen.Hier worden pulsen toegepast op EEPROM -cellen en de opgehaalde gegevens worden vergeleken met de verwachte waarden.Als er discrepanties worden gevonden, kan herprogrammering nodig zijn.Eindelijk de Exit ISP Stage zorgt ervoor dat de overgang van I/O -pins terug naar de gebruikersmodus, wat nog 1 ms vereist.De totale programmerings- of verificatietijd wordt beïnvloed door twee hoofdfactoren: pulstijd, vereist voor EEPROM Wissen, programmeren en leesbewerkingen en verschuivende tijd, die afhankelijk is van de TCK (testklok) frequentie en het aantal cycli dat nodig is om instructies, adressen en gegevens over te dragen.Aangezien verschillende ISP-compatibele apparaten verschillende aantallen EEPROM-cellen hebben, zijn zowel totale vaste als variabele tijden uniek voor elk apparaat.De totale ISP -tijd kan worden berekend als een functie van TCK -frequentie, het aantal doelapparaten en de EEPROM -architectuur.

EPM7064STC100-7 TOEPASSINGEN

Ingebedde systemen

De EPM7064STC100-7 wordt veel gebruikt in ingebedde systeemtoepassingen, waar het dient als een flexibele programmeerbare logische oplossing voor het besturen van verschillende randapparatuur, verwerkingssignalen en het implementeren van aangepaste protocollen.Het vermogen om te communiceren met microcontrollers en sensoren maakt het mogelijk om systeemprestaties te optimaliseren met behoud van een compacte voetafdruk.Met zijn snelle werking en een laag stroomverbruik is het een uitstekende keuze voor ingebedde toepassingen die betrouwbaarheid en efficiëntie vereisen.

Digitale signaalverwerking (DSP)

Bij digitale signaalverwerking speelt de EPM7064STC100-7 een rol bij het implementeren van filters, signaalmodulatie en verschillende wiskundige functies.De snelle schakelsnelheden en lage voortplantingsvertraging maken het geschikt voor het verwerken van hoogfrequente gegevensverwerkingstaken, waardoor minimale latentie in signaalconversie en manipulatie wordt gewaarborgd.Het wordt vaak gebruikt in audioverwerking, telecommunicatie en radarsystemen.

Datacommunicatie

De EPM7064Stc100-7 wordt uitgebreid gebruikt in netwerk- en datacommunicatiesystemen vanwege het vermogen om logica-intensieve bewerkingen te verwerken, zoals gegevensroutering, buffering en foutcorrectie.Door de programmeerbare I/O -mogelijkheden kan het zich aanpassen aan verschillende communicatieprotocollen, waardoor het een waardevol onderdeel is in Ethernet -schakelaars, routers en telecommunicatie -infrastructuur.De ondersteuning voor programmeerbaarheid van in-systemen (ISP) maakt ook veldupdates mogelijk, waardoor het aanpassingsvermogen in dynamische netwerkomgevingen wordt verbeterd.

Industriële automatisering

Industriële toepassingen vereisen hoge betrouwbaarheid, duurzaamheid en laag stroomverbruik, waardoor de EPM7064Stc100-7 een voorkeurskeuze is voor programmeerbare logische controllers (PLC's), motorbesturingssystemen en geautomatiseerde testapparatuur.Met zijn op JTAG gebaseerde programmeerbaarheid in het systeem biedt het de mogelijkheid om automatiseringsprocessen te verfijnen zonder fysieke verwijdering of herontwerp te vereisen.De veelzijdigheid in spanningscompatibiliteit maakt het ook geschikt om te interfaceren met een breed scala aan sensoren en actuatoren die worden gebruikt in industriële omgevingen.

EPM7064Stc100-7 vergelijkbare onderdelen

EPM7064STC100-7 Voordelen

System-programmeerbaarheid (ISP)

Een van de grootste voordelen van de EPM7064Stc100-7 is het vermogen om opnieuw te worden geprogrammeerd terwijl het nog steeds in het systeem is gemonteerd.Dit elimineert de noodzaak om de chip voor updates te verwijderen, de onderhoudstijd te verminderen en de efficiëntie te verbeteren.U kunt ontwerpaanpassingen implementeren zonder de productie te onderbreken, waardoor het een kosteneffectieve oplossing is voor projecten op lange termijn.

Snelle prestaties

Het apparaat ondersteunt een hoge interne bedrijfsfrequentie van maximaal 166,7 MHz, waardoor snelle gegevensverwerking en responstijden mogelijk zijn.Dit maakt het ideaal voor toepassingen waarvoor signaalverwerking, logische besturing en snelle interface-faillering vereist, waardoor een soepelere en betrouwbaardere systeembewerking wordt gewaarborgd.

Veelzijdige I/O -ondersteuning

Met maximaal 68 configureerbare I/O-pins en compatibiliteit met meerdere spanningsniveaus (3.3V, 5V en tolerante opties voor 2,5 V, 3.3V en 5V) biedt de EPM7064STC100-7 flexibiliteit in systeemontwerp.Het maakt naadloze integratie in verschillende circuits mogelijk en ondersteunt gemengde spanningsomgevingen, waardoor compatibiliteitsproblemen met andere componenten worden verminderd.

Betrouwbare werking in verschillende omgevingen

Ontworpen om te functioneren binnen een temperatuurbereik van 0 ° C tot 70 ° C, zorgt de EPM7064STC100-7 voor een consistente en stabiele werking in verschillende omstandigheden.Deze betrouwbaarheid maakt het een voorkeurskeuze voor toepassingen waar milieustabiliteit vereist is, zoals industriële automatisering, telecommunicatie en ingebedde besturingssystemen.

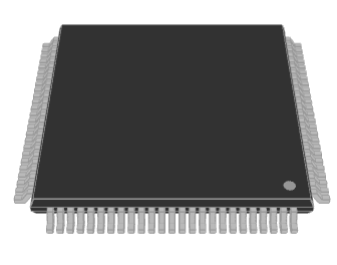

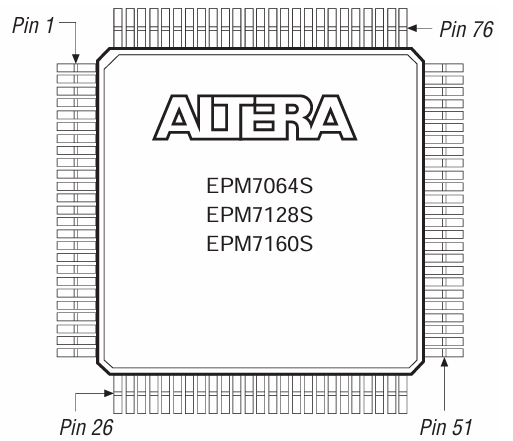

EPM7064STC100-7 PAKKET PIN-OUT DIAGRAM

De EPM7064STC100-7 is een CPLD (complex programmeerbaar logisch apparaat) uit Altera's Max 7000S-serie, gehuisvest in een 100-pins dun quad plat pakket (TQFP-100).Dit pakkettype is ontworpen voor applicaties op het oppervlak, en biedt een balans van hoge pindichtheid en compacte grootte.De pin-out diagram volgt een nummeringsschema tegen de klok in, met pin 1 in de linkerbovenhoek van het pakket.Tegen de klok in bewegend, bezetten de eerste 25 pinnen de linkerkant, pennen 26 tot 50 worden langs de onderkant geplaatst, pennen 51 tot 75 gaan verder langs de rechterkant en pinnen 76 tot 100 worden verspreid langs de bovenrand.De TQFP-100-pakket Beschikt over dunne leads die zich naar buiten uitstrekken van alle vier de zijden van het platte, vierkante lichaam.Dit ontwerp verbetert de compatibiliteit van het oppervlakte-montage met behoud van adequate pinafstand voor eenvoudig solderen en monteren.De loodsteld (afstand tussen aangrenzende pennen) is meestal 0,5 mm, waardoor de signaalintegriteit wordt geoptimaliseerd en de totale voetafdruk wordt geminimaliseerd.

EPM7064STC100-7 fabrikant

De EPM7064STC100-7 is een CPLD (complex programmeerbaar logisch apparaat) oorspronkelijk ontwikkeld door Altera, een halfgeleiderbedrijf dat bekend staat om zijn programmeerbare logische oplossingen.In 2015, Intel Verworven Altera, integratie van zijn FPGA- en CPLD -productlijnen in Intel's Programmable Solutions Group (PSG).Sindsdien is de EPM7064STC100-7 onder Intel gebrandmerkt, hoewel deze als verouderd is gemarkeerd.Intel, als fabrikant, handhaafde de Legacy -ondersteuning voor CPLD's van Max® 7000 -serie, inclusief dit model, terwijl hij geleidelijk zijn focus verlegt naar moderne FPGA en programmeerbare logische technologieën.

Conclusie

De EPM7064STC100-7 brengt complexe functies, snelle prestaties en eenvoudige updates in één chip samen, wat de waarde bewijst aan uitdagende digitale setups.Deze gids heeft aangetoond hoe het werkt, waarvoor het wordt gebruikt en hoe het past in verschillende elektronische systemen.Het helpt apparaten soepel en efficiënt te laten werken, wat bewijst dat het voor veel toepassingen nog steeds erg nuttig is.Deze gids biedt een duidelijk beeld van hoe de EPM7064STC100-7 kan helpen bij het effectief verbeteren van elektronische ontwerpen en systeembewerkingen.

Datasheet PDF

EPM7064STC100-7 Datasheets:

Over ons

ALLELCO LIMITED

Lees verder

Quick Inviry

Stuur een aanvraag, we zullen onmiddellijk reageren.

Veel Gestelde Vragen [FAQ]

1. Hoe wordt de vertraaging van 7,5ns voortplanting van de EPM7064Stc100-7 impactcircuitprestaties?

Een vertraaging van 7,5 ns voorstanders zorgt voor signaalverwerking met lage latentie, waardoor deze CPLD geschikt is voor snelle toepassingen zoals digitale signaalverwerking (DSP), communicatiesystemen en industriële automatisering die nauwkeurige timingcontrole vereisen.

2. Kan de EPM7064STC100-7 worden geprogrammeerd met behulp van moderne ontwikkelingstools?

Ja, het kan worden geprogrammeerd met behulp van Intel's Quartus II -software (voorheen Altera Quartus) samen met een geschikte JTAG -programmeur.Ondersteuning voor oudere CPLD's zoals de EPM7064STC100-7 kan echter beperkt zijn in nieuwere kwartsversies, dus u moet mogelijk oude versies zoals Quartus II 13.0 SP1 gebruiken, die nog steeds de MAX® 7000S-serie-apparaten ondersteunen.

3. Ondersteunt de EPM7064STC100-7 gemengde spanning omgevingen?

Ja, het ondersteunt zowel 3,3 V- als 5V -logische niveaus, waardoor het compatibel is met een breed scala aan digitale circuits.Deze flexibiliteit is nuttig voor het interfaceren van legacy 5V-componenten met moderne 3.3V-systemen zonder extra niveausverschuivingscircuits.

4. Wat is de beste methode voor het oplossen van een EPM7064Stc100-7-gebaseerd ontwerp?

Om problemen op te lossen, kunt u Quartus signaaltap II logische analysator of externe oscilloscopen en logische analysatoren gebruiken om signalen te controleren.Als debuggen van JTAG -programmeerproblemen, zorg er dan voor dat TDI-, TDO-, TCK- en TMS -verbindingen correct zijn en dat u een compatibele USB -blaster of byteblasterMV -programmeur gebruikt.

5. Kan ik de EPM7064STC100-7 programmeren zonder deze uit mijn printplaat te verwijderen?

Ja.Met de 5.0V programmeerbaarheid in het systeem (ISP) via JTAG (IEEE 1149.1) kunt u het apparaat herprogrammeren terwijl het in het systeem blijft.Dit maakt firmware -updates, foutopsporing en testen veel efficiënter in vergelijking met traditionele CPLD's.

Volledige gids voor de 10K -weerstand: kleurcode, toepassingen en circuitgebruik

Op 2025/03/10

Condensatoren versus batterijen: wat is het beste voor uw energiebehoeften?

Op 2025/03/7

Populaire berichten

-

Complexe instructieset computers: hoe ze de computer hebben gewijzigd?

Op 8000/04/18 147778

-

USB-C-pinout en functies

Op 2000/04/18 112032

-

Met behulp van Xilinx Unified Simulation Primitives: een uitgebreide gids voor FPGA -ontwerp en simulatie

Op 1600/04/18 111351

-

Voedingsspanningen in elektronica: betekenis van VCC, VDD, VEE, VSS en GND

Op 0400/04/18 83788

-

RJ45 -connectorhandleiding: pinout, bedrading, kabeltypen en gebruik

Op 1970/01/1 79589

-

De ultieme gids voor draadkleurcodes in moderne elektrische systemen

De manier waarop onze elektrische systemen kleuren gebruiken, is niet alleen voor uiterlijk.Elke draadkleur geeft nu een specifieke functie aan, waardoor het gemakkelijker wordt om elektrische comp...Op 1970/01/1 66973

-

PURGE VLEP GIDS: Functie, symptomen, testen en vervanging voor optimale motorprestaties

De Purge -klep is een belangrijk onderdeel van het systeem van een auto dat helpt de lucht schoon te houden door brandstofdampen te beheren voordat ze in de atmosfeer kunnen ontsnappen.Dit helpt ni...Op 1970/01/1 63109

-

Kwaliteit (Q) Factor: vergelijkingen en toepassingen

De kwaliteitsfactor, of 'Q', is belangrijk bij het controleren hoe goed inductoren en resonatoren werken in elektronische systemen die radiofrequenties gebruiken (RF).'Q' meet hoe goed een circuit ...Op 1970/01/1 63043

-

Piekprestaties bereiken met de maximale stelling van de stroomoverdracht

De maximale stelling van de stroomoverdracht legt uit hoe energie van een bron, zoals een batterij of generator, naar een aangesloten belasting stroomt.Het toont de exacte voorwaarde waar de belast...Op 1970/01/1 54097

-

A23 Batterijspecificaties en compatibiliteit

De A23-batterij is een kleine, cilindervormige batterij met hoge spanning.Ook wel 23A, 23ae of MN21 genoemd, het loopt op 12 volt en veel hoger dan AA- of AAA -batterijen.Het speciale ontw...Op 1970/01/1 52195