EP1C4F400C8 FPGA: functies, specificaties, programmering en alternatieven

Als u werkt met programmeerbare logica, geeft de EP1C4F400C8 u een praktisch evenwicht tussen prestaties en kosten.In dit artikel leert u wat deze FPGA is, de belangrijkste functies zoals logische capaciteit, geheugen en I/O -opties en hoe de structuur de betrouwbaar ontwerp ondersteunt.U ziet ook de specificaties, toepassingen in systemen, programmeerproces en hoe het zich verhoudt tot vergelijkbare onderdelen.Catalogus

Wat is de EP1C4F400C8?

De Sluit is lid van Intel's (voorheen Altera's) Cyclone FPGA-familie, ontworpen als een kosteneffectieve en betrouwbare programmeerbare logische oplossing.Gebouwd op een 0,13 µm SRAM-proces, biedt dit apparaat een matige logische dichtheid en flexibele I/O-opties binnen een compact FBGA-400-pakket.De Cyclone -familie, die apparaten zoals EP1C3, EP1C6, EP1C12 en EP1C20 omvat, is gemaakt om de prestaties en betaalbaarheid voor schaalbare ontwerpen in evenwicht te brengen, waardoor eenvoudige migratie tussen dichtheidsniveaus en pakketten mogelijk is.Bekend om stabiliteit en brede acceptatie, blijft het een vertrouwde keuze in legacy -ontwerpen.

Op zoek naar EP1C4F400C8?Neem contact met ons op om de huidige voorraad, doorlooptijd en prijzen te controleren.

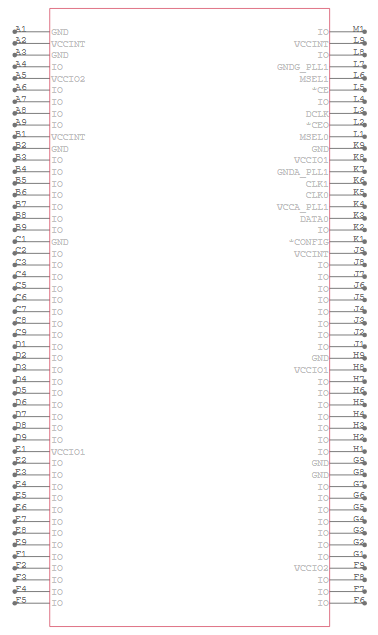

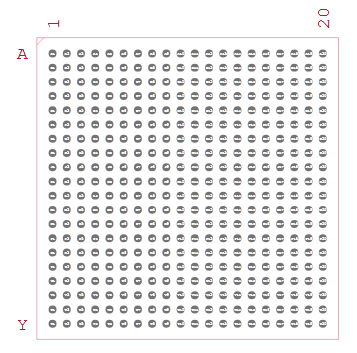

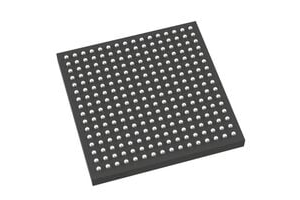

EP1C4F400C8 CAD -modellen

EP1C4F400C8 -symbool

EP1C4F400C8 voetafdruk

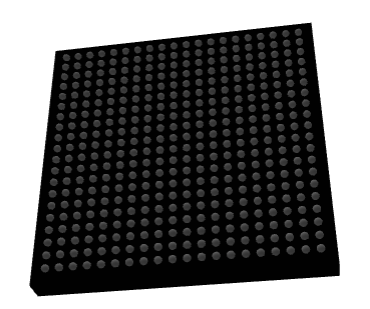

EP1C4F400C8 3D -model

EP1C4F400C8 -functies

• Logische capaciteit

De EP1C4F400C8 biedt ongeveer 4.000 logische elementen, georganiseerd in 400 logische arrayblokken (labs).Dit maakt het geschikt voor ontwerpen in de middellange afstand die gematigde logische dichtheid vereisen met behoud van de kostenefficiëntie.

• Ingebed geheugen

Het integreert ongeveer 76,5 kbits ingebed geheugen.Dit interne RAM ondersteunt gegevensbuffering, opslag en kleine geheugenfuncties, waardoor de behoefte aan externe geheugencomponenten in veel ontwerpen wordt verminderd.

• Hoge I/O -telling

Het apparaat biedt 301 gebruikers-configureerbare I/O-pinnen in het 400-ball FBGA-pakket.Deze hoge pin -telling maakt rijke connectiviteit mogelijk voor complexe systemen die meerdere perifere interfaces vereisen.

• Brede I/O -normenondersteuning

Het ondersteunt meerdere I/O-normen, waaronder LVTTL, LVCMOS, SSTL-2, SSTL-3 en differentiële LVD's.Met deze flexibiliteit kan de FPGA rechtstreeks communiceren met een verscheidenheid aan moderne logische families en geheugenapparaten.

• High-speed differentiaalsignalering

Met LVD's ondersteuning tot 640 Mbps, behandelt de FPGA snelle gegevensoverdrachtseisen.Dit maakt het praktisch voor toepassingen zoals hoogsnelheid communicatieverbindingen en snelle digitale interfaces.

• Klokbeheer met PLLS

De chip integreert twee fase-vergrendelde lussen (PLL's) en acht wereldwijde kloknetwerken.Deze functies maken precieze klokgeneratie, vermenigvuldiging en jitterbesturing mogelijk voor timing-kritische toepassingen.

• Laagspanningskernbewerking

Werk bij een nominale 1,5 V -kernspanning, brengt het apparaat de prestaties in evenwicht met een lager stroomverbruik.Dit spanningsniveau werd geoptimaliseerd voor de 0,13-µm CMOS-technologie die in zijn fabricage werd gebruikt.

• Flexibele I/O -spanningen

De FPGA ondersteunt I/O -spanningen van 1,5 V, 1,8 V, 2,5 V en 3,3 V bij verschillende banken.Deze veelzijdigheid stelt het in staat om te communiceren met zowel legacy- als moderne systeemcomponenten.

• Op SRAM gebaseerde configuratie

Net als andere cycloon FPGA's is het op SRAM gebaseerd en vereist het opnieuw configureren bij elke power-up.Dit biedt flexibiliteit voor updates, maar vereist ook een extern configuratieapparaat of controller.

• Bitstream compressieondersteuning

De EP1C4F400C8 ondersteunt gecomprimeerde bitstream -lading tijdens de configuratie.Dit vermindert externe geheugenvereisten en versnelt de configuratietijden.

• PCI -naleving

Het bevat ingebouwde ondersteuning voor PCI-normen (33/66 MHz, 32/64-bit).Met deze functie kan het apparaat rechtstreeks worden geïntegreerd in systemen die PCI -interface moeten vereisen zonder extra overbruggen.

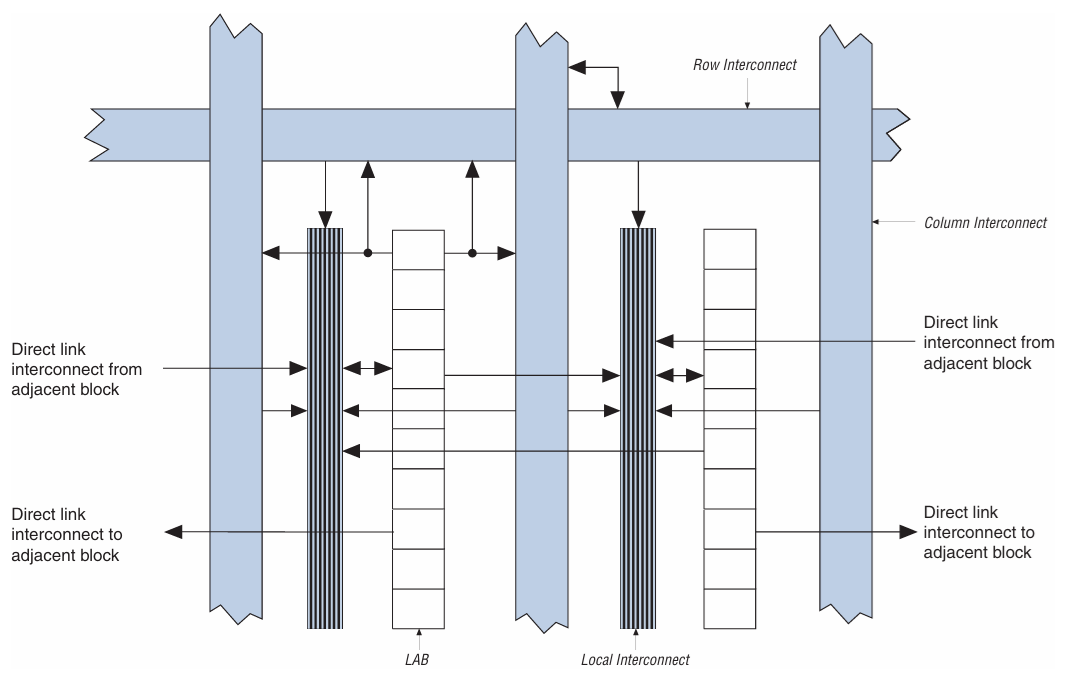

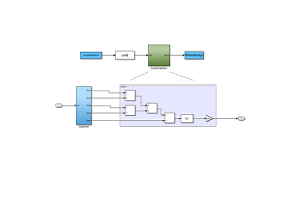

Cyclone Lab structuur

Het diagram toont de structuur van de logische arrayblok (lab) die wordt gebruikt in cycloon FPGA's zoals de EP1C4F400C8.Elk laboratorium maakt verbinding met een netwerk van interconnects: rij interconnects, kolomverbindingen en lokale interconnects, die signalen tussen logische elementen en andere blokken routeren.Directe verbindingen van links bieden snelle paden met lage latentie naar aangrenzende laboratoria, waardoor de timingprestaties in signaalpaden worden verbeterd.Deze architectuur is belangrijk omdat het routeflexibiliteit in evenwicht brengt met efficiëntie, waardoor de FPGA complexe ontwerpen kan verwerken, terwijl de snelheid en het gebied geoptimaliseerd blijven.

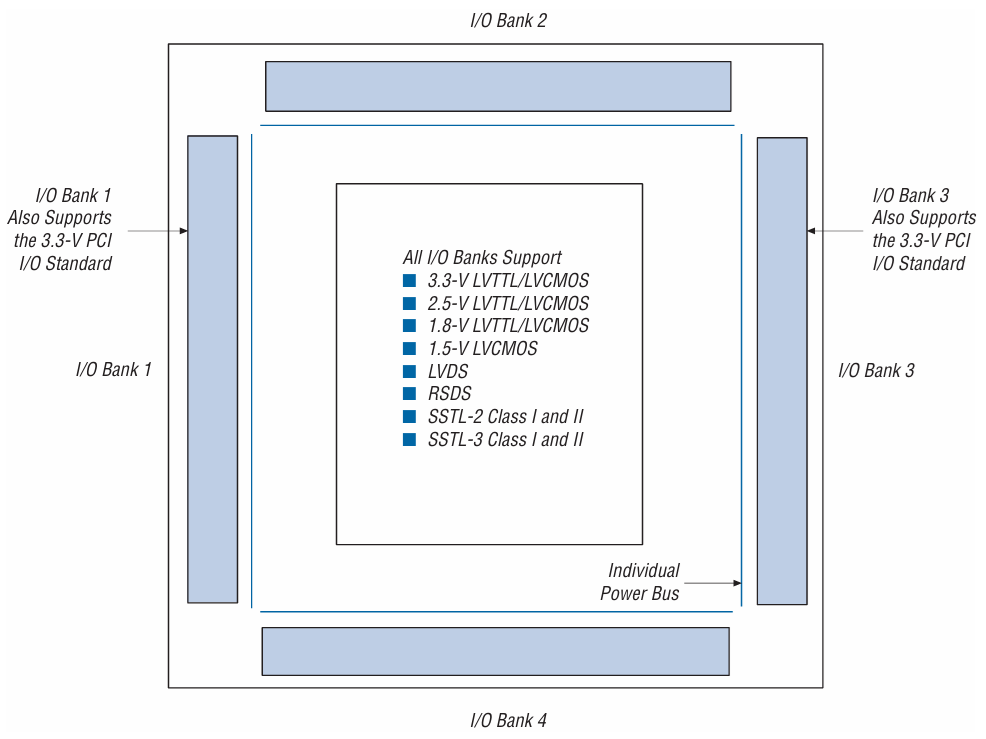

Cycloon I/O Banks -diagram

Het diagram illustreert de I/O -bankstructuur van cycloon FPGA's zoals de EP1C4F400C8.Het apparaat is verdeeld in vier I/O -banken, elk aangedreven door zijn eigen voedingsbus, waardoor verschillende spanningsnormen binnen een enkele FPGA kunnen worden gecombineerd.Alle banken ondersteunen een breed scala aan I/O-normen, waaronder LVTTL, LVCMOS, LVDS, RSDS en SSTL, terwijl banken 1 en 3 ook 3,3-V PCI ondersteunen voor compatibiliteit met legacy-systemen.Deze flexibele I/O -architectuur is belangrijk omdat het naadloze integratie met diverse externe apparaten en interfaces mogelijk maakt, waardoor de FPGA zich kan aanpassen aan verschillende toepassingen.

EP1C4F400C8 specificaties

|

Type |

Parameter |

|

Fabrikant |

Altera/intel |

|

Serie |

Cyclone® |

|

Verpakking |

Dienblad |

|

Onderdeelstatus |

Verouderd |

|

Aantal laboratorium/CLB's |

400 |

|

Aantal logische elementen/cellen |

4000 |

|

Totaal rambits |

78,336 |

|

Aantal I/O |

301 |

|

Spanning - levering |

1.425V ~ 1.575V |

|

Montagetype |

Oppervlaktemontage |

|

Bedrijfstemperatuur |

0 ° C ~ 85 ° C (TJ) |

|

Pakket / kast |

400-BGA |

|

Leverancierapparaatpakket |

400-FBGA (21 × 21) |

|

Base Productnummer |

EP1C4 |

EP1C4F400C8 -toepassingen

1. Digitale signaalverwerking (DSP)

De EP1C4F400C8 kan worden geprogrammeerd om taken uit te voeren zoals filteren, FFT's en signaalmodulatie.De combinatie van logische elementen en ingebed geheugen maakt het geschikt voor snelle verwerking.Hierdoor kan het traditionele DSP -chips vervangen door een flexibele FPGA -oplossing die kan worden herprogrammeerd voor verschillende algoritmen.

2. Ingebed en besturingssystemen

In industriële en ingebedde systemen wordt deze FPGA vaak gebruikt om aangepaste controllers, sequencers en staatsmachines te implementeren.De herconfigureerbare logica maakt het mogelijk om hardwaregedrag aan te passen, juist op systeembehoeften.Door de controlelogica in de FPGA te integreren, wordt het aantal externe componenten verlaagd, waardoor de betrouwbaarheid en de verlagingskosten worden verbeterd.

3. Communicatie en interface overbruggen

Het apparaat ondersteunt meerdere I/O -normen en kan fungeren als een brug tussen verschillende communicatieprotocollen.Het wordt vaak gebruikt om PCI, LVD's, SDRAM en andere interfaces naadloos binnen een systeem aan te sluiten.Dit maakt het zeer nuttig in netwerkapparatuur, ingebedde controllers en legacy-naar-moderne interface-conversies.

4. Data -acquisitie en -verwerking

Met een hoge I/O-beschikbaarheid en flexibel geheugen is de EP1C4F400C8 zeer geschikt voor gegevensverzamelingssystemen.Het kan direct communiceren met ADC's en sensoren, de gegevens op tijd verwerken en voorbereiden op opslag of verzending.Dergelijke toepassingen zijn gebruikelijk in medische instrumenten, testapparatuur en wetenschappelijke meetapparaten.

EP1C4F400C8 vergelijkbare onderdelen

|

Specificatie |

Sluit |

EP1C4F400C8N |

EP1C4F400C8NAAA |

EP1C4F400C6N |

EP1C4F324C8N |

EP1C4T144C8N |

|

Fabrikant |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

|

FPGA -familie |

Cycloon (EP1C4) |

Cycloon (EP1C4) |

Cycloon (EP1C4) |

Cycloon (EP1C4) |

Cycloon (EP1C4) |

Cycloon (EP1C4) |

|

Logica -elementen (LES) |

4.000 |

4.000 |

4.000 |

4.000 |

4.000 |

4.000 |

|

Embedded Memory (bits) |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

|

I/O -pinnen |

301 |

301 |

301 |

301 |

249 |

97 |

|

Pakket / kast |

400-FBGA |

400-FBGA |

400-FBGA |

400-FBGA |

324-FBGA |

144-tqfp |

|

Snelheidsgraad |

C8 |

C8 |

C8 |

C6 (sneller) |

C8 |

C8 |

|

Kernspanning |

1.5 V |

1.5 V |

1.5 V |

1.5 V |

1.5 V |

1.5 V |

|

Operationele temp.Bereik |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C

|

EP1C4F400C8 programmeerstappen

Voordat u de EP1C4F400C8 FPGA kunt gebruiken, moet u uw ontwerp in het apparaat laden.Programmering omvat het configureren van de FPGA met een bitstream -bestand, zodat het weet hoe ze zich moeten gedragen als uw beoogde circuit.

1. Selecteer Configuratieschema en stel MSEL -pins in

U begint met het kiezen van het configuratieschema dat het beste bij uw installatie past, zoals actieve seriële, passieve serie of JTAG.Dit wordt gedaan door de MSEL-pins in te stellen op specifieke logische niveaus vóór het opstarten.Elke modus maakt gebruik van verschillende pinnen en protocollen, dus u moet de compatibiliteit bevestigen met uw ontwerptools en configuratie -geheugen.Het maken van de juiste keuze hier zorgt voor een soepel configuratieproces.

2. Pas stroom aan en initialiseer het apparaat

Voeg vervolgens de kern van de FPGA en I/O -rails op binnen de opgegeven spanningsbereiken.Houd tijdens het opstarten de Nconfig -pin laag om het apparaat in reset te houden totdat de voedingsspanningen stabiel zijn.Eenmaal stabiel, laat u de reset vrij en geeft het apparaat de gereedheid aan door de nstatus -pin te besturen.Dit garandeert dat de FPGA correct wordt geïnitialiseerd voordat de configuratie begint.

3. Verzend de configuratie bitstream

In dit stadium stuurt u het configuratiegegevensbestand (Bitstream) naar de FPGA met behulp van uw geselecteerde schema.In de actieve seriële of passieve seriële modus komt de bitstream van een extern geheugenapparaat, terwijl JTAG directe programmering via kabel mogelijk maakt.Het apparaat leest continu in de configuratiegegevens totdat het is voltooid.Uw ontwerpsoftware genereert deze bitstream om aan uw logische vereisten te voldoen.

4. Bevestig succesvolle configuratie (conf_done)

Wanneer de FPGA het laden voltooit, beweert deze de conf_done -pin om aan te tonen dat configuratiegegevens met succes zijn ontvangen.Tegelijkertijd voert het apparaat interne initialisatie uit, zoals het wissen van registers en het activeren van I/O.Als conf_done niet hoog wordt, betekent dit meestal dat de configuratiegegevens of instellingen een fout hebben.Het bekijken van deze pin is de eenvoudigste manier om te controleren of het proces voltooid is.

5. Voer optionele herconfiguratie in system uit

Ten slotte hebt u de optie om de FPGA bij te werken of te herprogrammeren zonder deze uit het bord te verwijderen.Met behulp van JTAG of een ingesloten controller kunt u een nieuwe bitstream rechtstreeks laden, wat handig is voor firmware -updates.Met deze flexibiliteit kunt u uw systeem wijzigen, debuggen of upgraden, zelfs na de implementatie.Het zorgt ervoor dat uw op FPGA gebaseerde ontwerp zich in de loop van de tijd kan aanpassen aan het wijzigen van vereisten.

EP1C4F400C8 -voor- en nadelen

Voordelen

• kostenefficiënte keuze voor ontwerpen in de middellange afstand

• Hoge I/O -telling vergeleken met vergelijkbare dichtheidsapparaten

• Flexibele spanning en I/O standaardondersteuning

• Gesteund door volwassen tools en documentatie

• Lager vermogensgebruik dan oudere FPGA -generaties

Nadelen

• Verouderd met beperkte beschikbaarheid op lange termijn

• Lagere logica en geheugencapaciteit versus moderne FPGA's

• Lagere bedrijfssnelheid en I/O -prestaties

• Vereist extern geheugen voor configuratie op power-up

• Ontbreekt geavanceerde functies zoals DSP-blokken en high-speed transceivers

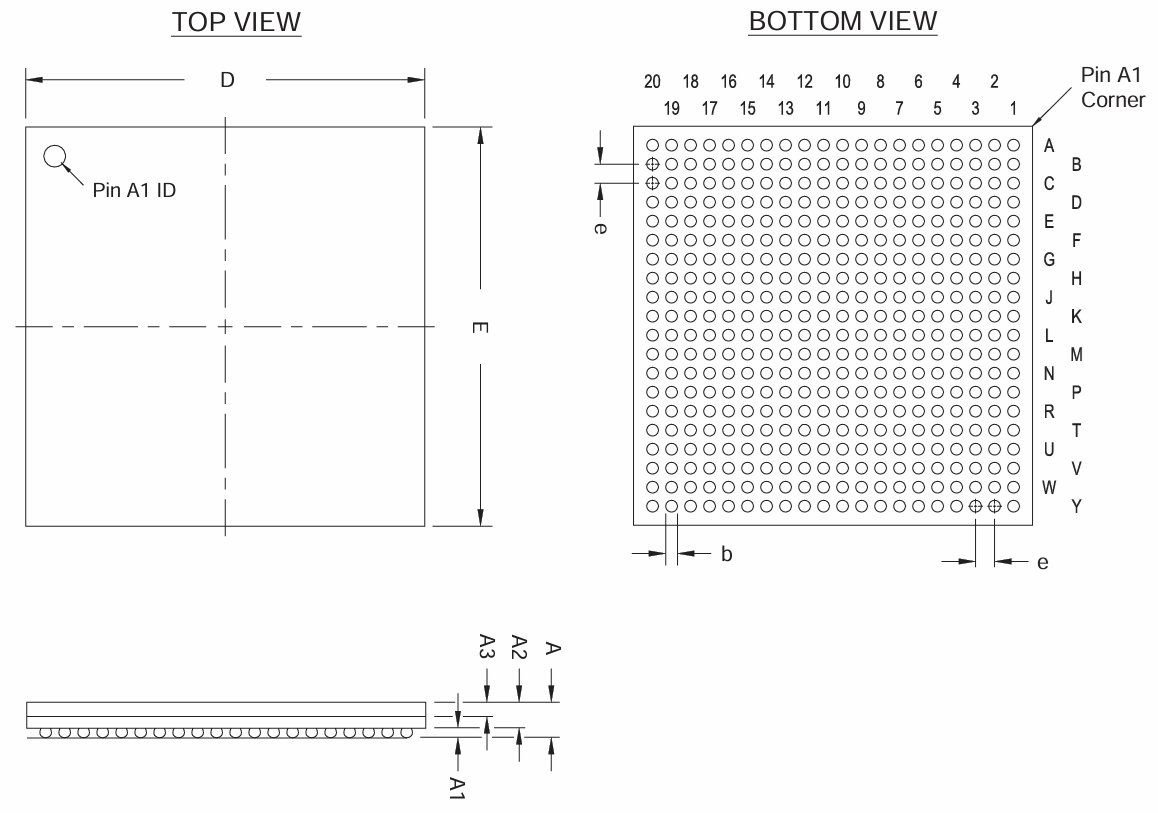

EP1C4F400C8 verpakkingsafmetingen

|

Type |

Parameter |

|

Pakkettype |

FBGA (Fine-Pitch Ball Grid Array) |

|

Bal telling |

400 |

|

Balveld (e) |

1,0 mm (typisch voor cycloon EP1C4F400) |

|

Kogeldiameter (b) |

0,45 mm (nominaal) |

|

Pakketmaat (D × E) |

21 mm × 21 mm |

|

Pakkethoogte (a) |

2,40 mm (max) |

|

Substraatdikte (A2) |

~ 0,40 mm |

|

Dikte van schimmel dop (a3) |

~ 1,90 mm |

|

Kogelhoogte (a1) |

0,25 mm (nominaal) |

|

Pin A1 Corner |

Gemiddeld voor oriëntatie |

|

Array lay -out |

20 × 20 rooster (met hoekballen ontbreken) |

|

Montage |

Surface Mount (SMD) |

EP1C4F400C8 fabrikant

De EP1C4F400C8 werd oorspronkelijk vervaardigd door Altera Corporation, een pionier in programmeerbare logische apparaten en FPGA -technologie.In 2015 werd Altera overgenomen door Intel Corporation, en de productlijn werd onderdeel van Intel's Programmable Solutions Group (PSG).Tegenwoordig ondersteunt Intel deze legacy altera -apparaten terwijl hij de ontwikkeling op nieuwere FPGA -families concentreert, zorgt voor continuïteit voor bestaande gebruikers en het bevorderen van innovatie in programmeerbare logica.

Conclusie

De EP1C4F400C8 valt op als een kostenefficiënte en veelzijdige FPGA die solide prestaties biedt voor ontwerpen in het middenbereik.Met zijn 4.000 logische elementen, ingebed geheugen, uitgebreide I/O -ondersteuning en compatibiliteit met meerdere spanning- en interfacestandaarden, biedt het flexibiliteit in verschillende toepassingen.De architectuur, het programmeerproces en de brede bruikbaarheid in DSP, ingebedde systemen en data -acquisitie maken het een praktische keuze ondanks zijn oude status.Hoewel het geen geavanceerde functies mist die in nieuwere apparaten te vinden zijn en beperkte langetermijnbeschikbaarheid wordt geconfronteerd, blijft het een betrouwbare optie om bewezen oplossingen te zoeken in schaalbare FPGA-ontwerpen.

Datasheet PDF

EP1C4F400C8 Datasheets:

Over ons

ALLELCO LIMITED

Lees verder

Quick Inviry

Stuur een aanvraag, we zullen onmiddellijk reageren.

Veel Gestelde Vragen [FAQ]

1. Welke tools zijn vereist om de EP1C4F400C8 te programmeren?

U hebt Intel's Quartus-software (voorheen Altera Quartus II) nodig, samen met een ondersteunde programmeerkabel zoals USB-Blaster.Met deze tools kunt u de bitstream maken en in de FPGA laden.

2. Kan de EP1C4F400C8 PCI -toepassingen direct verwerken?

Ja, het heeft een ingebouwde naleving van PCI-normen (33/66 MHz, 32/64-bit), waardoor het geschikt is voor PCI-gebaseerde systeemintegratie zonder extra overbruggende logica.

3. Wat gebeurt er als de EP1C4F400C8 mislukt tijdens de configuratie?

Als de configuratie mislukt, wordt de conf_done -pin niet hoog geleverd.Dit wijst meestal op een fout in het bitstream -bestand, spanningssequencing of pin -instellingen en moet opnieuw worden gecontroleerd in uw ontwerpstroom.

4. Kan de EP1C4F400C8 -interface rechtstreeks met DDR -geheugen interface?

Het ondersteunt verschillende I/O -normen, maar heeft geen native DDR -interfaces zoals moderne FPGA's.Aanvullende ontwerpoverwegingen of overbruggende componenten kunnen nodig zijn.

5. Hoe verhoudt de EP1C4F400C8 zich tot nieuwere FPGA's?

In vergelijking met moderne apparaten heeft de EP1C4F400C8 een lagere snelheid, minder logische dichtheid en minder geavanceerde functies.Het blijft echter een kostenefficiënte keuze voor stabiele, mid-range ontwerpen waar geavanceerde prestaties niet vereist zijn.

EPM3256AFC256-7 CPLD-overzicht: Functies, Pinout, programmeren en applicaties

Op 2025/10/3

ADG432BR Analog Switch IC: specificaties, pinout, alternatieven en datasheet

Op 2025/10/2

Populaire berichten

-

Complexe instructieset computers: hoe ze de computer hebben gewijzigd?

Op 8000/04/18 147772

-

USB-C-pinout en functies

Op 2000/04/18 112009

-

Met behulp van Xilinx Unified Simulation Primitives: een uitgebreide gids voor FPGA -ontwerp en simulatie

Op 1600/04/18 111351

-

Voedingsspanningen in elektronica: betekenis van VCC, VDD, VEE, VSS en GND

Op 0400/04/18 83768

-

RJ45 -connectorhandleiding: pinout, bedrading, kabeltypen en gebruik

Op 1970/01/1 79565

-

De ultieme gids voor draadkleurcodes in moderne elektrische systemen

De manier waarop onze elektrische systemen kleuren gebruiken, is niet alleen voor uiterlijk.Elke draadkleur geeft nu een specifieke functie aan, waardoor het gemakkelijker wordt om elektrische comp...Op 1970/01/1 66960

-

PURGE VLEP GIDS: Functie, symptomen, testen en vervanging voor optimale motorprestaties

De Purge -klep is een belangrijk onderdeel van het systeem van een auto dat helpt de lucht schoon te houden door brandstofdampen te beheren voordat ze in de atmosfeer kunnen ontsnappen.Dit helpt ni...Op 1970/01/1 63100

-

Kwaliteit (Q) Factor: vergelijkingen en toepassingen

De kwaliteitsfactor, of 'Q', is belangrijk bij het controleren hoe goed inductoren en resonatoren werken in elektronische systemen die radiofrequenties gebruiken (RF).'Q' meet hoe goed een circuit ...Op 1970/01/1 63040

-

Piekprestaties bereiken met de maximale stelling van de stroomoverdracht

De maximale stelling van de stroomoverdracht legt uit hoe energie van een bron, zoals een batterij of generator, naar een aangesloten belasting stroomt.Het toont de exacte voorwaarde waar de belast...Op 1970/01/1 54097

-

A23 Batterijspecificaties en compatibiliteit

De A23-batterij is een kleine, cilindervormige batterij met hoge spanning.Ook wel 23A, 23ae of MN21 genoemd, het loopt op 12 volt en veel hoger dan AA- of AAA -batterijen.Het speciale ontw...Op 1970/01/1 52184