CPLD legde uit: een gids voor programmeerbare logica -apparaten

In de dynamische wereld van elektronisch ontwerp vallen complexe programmeerbare logica -apparaten (CPLD's) op als veelzijdige tools, naadloos aanpassingsvermogen, precisie en efficiëntie combineren.Deze apparaten hebben een revolutie teweeggebracht in het circuitontwerp door programmeerbare macrocellen en een dominante interconnectmatrix te introduceren, waardoor ingewikkelde logische functies met opmerkelijke betrouwbaarheid mogelijk zijn.Van hun oprichting in de jaren tachtig tot hun sleutelrol in moderne industrieën zoals netwerken, automotive en ruimtevaart, CPLD's hebben gebleken dat u zowel flexibiliteit als prestaties zoekt.Dit artikel graaft in de reis van CPLD's, hun onderscheidende kenmerken, praktische toepassingen en de programmeermethoden die hen een hoeksteen maken in digitaal logisch ontwerp.Catalogus

Overzicht van CPLD

Binnen de heerschappij van complexe programmeerbare logische apparaten (CPLD's) ontdekt men een geavanceerd tapijt van programmeerbare logische macrocellen, verweven door een dominante interconnectmatrix.Met deze macrocel (MC) en invoer/uitvoer (I/O) -eenheid kunt u u in staat om behendig ontwerpen van circuits te ontwerpen en de structuren voor unieke functies te configureren.In tegenstelling tot apparaten die perplex zijn door hun ingewikkelde interconnect timing, gebruiken CPLD's onbeweegbare metalen draden.Dit kenmerk schenkt hen een consistent en voorzienbaar klokgedrag, waardoor timingvoorspellingen betrouwbaarder en nauwkeuriger worden.

De reis en het gebruik

De jaren 1970 luidden de komst van programmeerbare logica -apparaten (PLD's) in, en bevorderde een beweging naar programmeerbare macro -eenheden.Deze verschuiving introduceerde voldoende ontwerpflexibiliteit en onderscheidde ze van statische digitale circuits, hoewel hun nut aanvankelijk was beperkt tot eenvoudiger circuits.De komst van CPLD's in het midden van de jaren tachtig bracht dit landschap een revolutie teweeg in de weg voor complexe circuitontwerpen.Sindsdien hebben ze zich verweven in de structuur van industrieën zoals netwerken, automotive -elektronica, CNC -bewerking en ruimtevaartsystemen.U kunt herinneren aan de manier waarop CPLD's vereenvoudigde processen die ooit zorgvuldige handarbeid eisten, een opmerkelijke sprong in efficiëntie markeren.

Onderscheidende kwaliteiten van CPLD's

CPLD's onderscheiden zich door hun aanpasbare programmering, uitgebreide integratie, snelle ontwikkelingsmogelijkheden en brede toepasbaarheid, samen met economische productiekosten.Ze doen een beroep op mensen met minimale hardware -ervaring en dienen als betrouwbare en beveiligde producten die geen uitputtende testen vereisen.Als een bewijs van hun bekwaamheid in grootschalige circuitontwerpen, spelen CPLD's een sleutelrol in de ontwikkeling van prototype en dienen ze runs onder de 10.000 eenheden, die een nuttige competentie voor u belichamen.De vaardigheid waarmee CPLD's zich aanpassen aan het evolueren van projecteisen, verdient vaak waardering, en benadrukt hun werkelijke veelzijdigheid in dynamische omgevingen.

Toepassingsmethoden

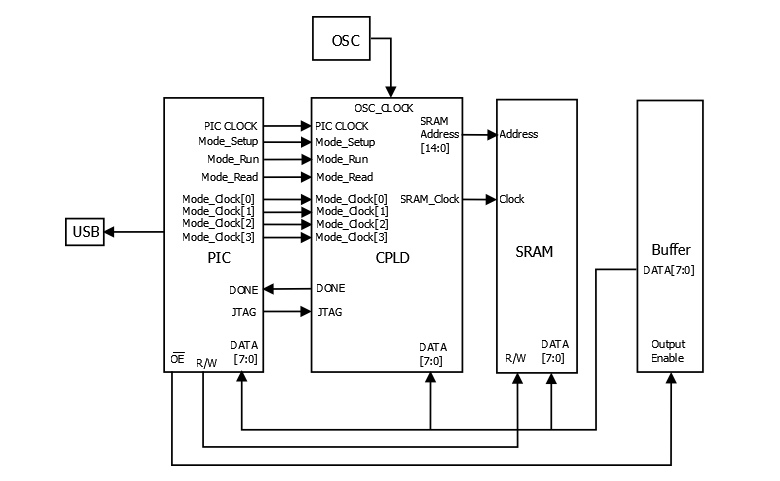

Met deze geïntegreerde circuits kunt u zich uitwerken op logische functies die zijn afgestemd op hun behoeften met behulp van zowel schema's als hardwarebeschrijving talen op ontwikkelingsplatforms.Bij het ontwerpen van een antwoordapparaat worden bijvoorbeeld schema's en hardwarebeschrijvingen op een computer voorbereid en opgesteld.Met behulp van een downloadkabel wordt de code overgedragen naar de CPLD voor programmering in system, die testen, probleemoplossing en het verbeteren van ontwerpen omvat.Succesvol vervaardigde ontwerpen worden vervolgens in massa geproduceerd door CPLD-chips te repliceren.In projecten zoals verkeerslichtsystemen wordt het herhalen van het ontwerpproces vereist, vergelijkbaar met het herbouwen van een huis om zijn nieuwheid te herstellen.Deze repetitieve methodologie legt vaak de basis voor mastering, waardoor zowel vaardigheden als vertrouwen worden vergroot.

Toonaangevende varianten

Door de jaren heen hebben bedrijven als Altera, Lattice en Xilinx prominente lijnen van CPLD's onthuld.Opmerkelijke voorbeelden zijn Altera's EPM7128S, Lattice's LC4128Ven Xilinx's XC95108 .Deze modellen hebben prominente rollen gevonden in verschillende wereldwijde toepassingen.Degenen die het voorrecht hebben gehad om met deze verschillende producten te werken, merken vaak op over de subtiele maar krachtige verschillen die bepaalde functionaliteiten optimaliseren.Dit weerspiegelt een mooi selectieproces dat wordt beïnvloed door specifieke projecteisen, waarbij elke variant zijn unieke aantrekkingskracht heeft.

Identificatie en classificatie van FPGA en CPLD

|

Aspect |

CPLD |

FPGA |

|

Logische gedragsvorming |

Vorm logisch gedrag met behulp van producttermstructuur.

Voorbeelden: rooster ISPLSI -serie, Xilinx XC9500 -serie, Altera Max7000s

serie, rooster mach -serie |

Vorm logisch gedrag met behulp van een tabelopzoekingsmethode.

Voorbeelden: Xilinx Spartan -serie, Altera Flex10K, ACEX1K -serie |

|

Geschiktheid |

Geschikt voor algoritmen en combinatielogica, werken

Beter met beperkte triggers en rijke productvoorwaarden |

Geschikt voor sequentiële logica, werkt beter met

Structuren rijk aan triggers |

|

Timingvertraging |

Continue bedradingsstructuur biedt uniforme en

voorspelbare timingvertragingen |

Gesegmenteerde bedradingsstructuur leidt tot onvoorspelbare timing

vertragingen |

|

Flexibiliteit programmeren |

Vaste interne circuits worden gewijzigd voor programmering.

Logica blokniveau programmeren wordt gebruikt |

Interne bedrading is gewijzigd voor programmeren.Logica

Programmering op poortniveau maakt een grotere flexibiliteit mogelijk |

|

Integratie |

Lagere integratie in vergelijking met FPGA |

Hogere integratie met een complexere bedradingsstructuur en

Logica -implementatie |

|

Gebruiksgemak |

Gemakkelijker te gebruiken met programmeren via E2PROM of FASTFLASH.

Er is geen externe geheugenchip vereist |

Vereist extern geheugen om programmeren op te slaan

informatie, wat leidt tot complexer gebruik |

|

Snelheid en voorspelbaarheid |

Hogere snelheid en betere voorspelbaarheid van timing vanwege

Gevulde interconnectie tussen logische blokken |

Lagere snelheid en minder voorspelbare timing vanwege

Gate-niveau programmering en gedistribueerde interconnectie |

|

Programmeertechnologie |

Gebruikt E2PROM- of Flash -geheugenprogrammering.Programmeergegevens

wordt behouden wanneer het systeem wordt uitgeschakeld.Ondersteunt programmeren op een

programmeur of in-system |

Gebaseerd op SRAM -programmering.Programmeergegevens gaan verloren wanneer

Het systeem wordt uitgeschakeld en moet opnieuw worden geladen.Ondersteunt Dynamic

configuratie |

|

Vertrouwelijkheid |

Biedt een betere vertrouwelijkheid |

Biedt een lagere vertrouwelijkheid |

|

Stroomverbruik |

Over het algemeen een hoger stroomverbruik, vooral met

Hogere integratie |

Lager stroomverbruik in vergelijking met CPLD |

Programmeertalen van CPLD

Analyse van hoe complexe programmeerbare logische apparaten (CPLD's) zijn geprogrammeerd, is een hoeksteen in het maken van veelzijdige hardware -oplossingen.De historische methoden voor het programmeren van CPLD's zijn afhankelijk van ladderdiagrammen of hardwarebeschrijving talen (HDL's), waarbij Verilog HDL en VHDL overheersende keuzes zijn.De geselecteerde taal kan zowel de ontwerpstrategie als de operationele efficiëntie van implementaties vormen.

• Verilog HDL: Verilog HDL wordt gekoesterd vanwege zijn eenvoudige syntaxis en robuuste simulatiemogelijkheden, die de methodologieën weerspiegelen die worden gebruikt in digitaal logisch ontwerp.De integratie met elektronische ontwerpautomatisering (EDA) -hulpmiddelen kunt u naadloos synthese en simulatie uitvoeren.Er is waargenomen dat de C-achtige syntaxis van Verilog de toetredingsdrempel voor mensen met programmeerachtergronden verlagen, waardoor de reis van het ontwerp naar de implementatie in een breed scala van industriële sectoren wordt bespoedigd.

• VHDL: VHDL biedt een meer uitgebreide en expressieve optie voor HDL -programmering.Het is vaak de keuze voor projecten die nauwgezette documentatie en rigoureuze typecontrole, eigenschappen die worden gewaardeerd in de ruimtevaart- en defensie-industrie eisen.U kunt opmerken dat ondanks de potentiële complexiteit van VHDL in kleinere projecten, de gedisciplineerde structuur het creëren van uitzonderlijk betrouwbare ontwerpen, een noodzaak in omgevingen waar de veiligheid dominant is.

Over ons

ALLELCO LIMITED

Lees verder

Quick Inviry

Stuur een aanvraag, we zullen onmiddellijk reageren.

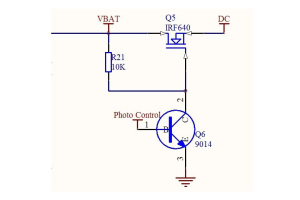

NMOS -transistors: ontwerp, bediening en toepassingen

Op 2024/12/29

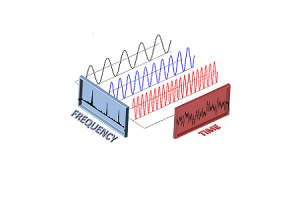

The Fast Fourier Transform (FFT): revolutionering van digitale signaalverwerking

Op 2024/12/29

Populaire berichten

-

Complexe instructieset computers: hoe ze de computer hebben gewijzigd?

Op 8000/04/18 147758

-

USB-C-pinout en functies

Op 2000/04/18 111956

-

Met behulp van Xilinx Unified Simulation Primitives: een uitgebreide gids voor FPGA -ontwerp en simulatie

Op 1600/04/18 111349

-

Voedingsspanningen in elektronica: betekenis van VCC, VDD, VEE, VSS en GND

Op 0400/04/18 83725

-

RJ45 -connectorhandleiding: pinout, bedrading, kabeltypen en gebruik

Op 1970/01/1 79508

-

De ultieme gids voor draadkleurcodes in moderne elektrische systemen

De manier waarop onze elektrische systemen kleuren gebruiken, is niet alleen voor uiterlijk.Elke draadkleur geeft nu een specifieke functie aan, waardoor het gemakkelijker wordt om elektrische comp...Op 1970/01/1 66922

-

PURGE VLEP GIDS: Functie, symptomen, testen en vervanging voor optimale motorprestaties

De Purge -klep is een belangrijk onderdeel van het systeem van een auto dat helpt de lucht schoon te houden door brandstofdampen te beheren voordat ze in de atmosfeer kunnen ontsnappen.Dit helpt ni...Op 1970/01/1 63078

-

Kwaliteit (Q) Factor: vergelijkingen en toepassingen

De kwaliteitsfactor, of 'Q', is belangrijk bij het controleren hoe goed inductoren en resonatoren werken in elektronische systemen die radiofrequenties gebruiken (RF).'Q' meet hoe goed een circuit ...Op 1970/01/1 63017

-

Piekprestaties bereiken met de maximale stelling van de stroomoverdracht

De maximale stelling van de stroomoverdracht legt uit hoe energie van een bron, zoals een batterij of generator, naar een aangesloten belasting stroomt.Het toont de exacte voorwaarde waar de belast...Op 1970/01/1 54086

-

A23 Batterijspecificaties en compatibiliteit

De A23-batterij is een kleine, cilindervormige batterij met hoge spanning.Ook wel 23A, 23ae of MN21 genoemd, het loopt op 12 volt en veel hoger dan AA- of AAA -batterijen.Het speciale ontw...Op 1970/01/1 52153